CRC 校验:从原理到实现(二)

1、收发端CRC校验的可选机制

CRC校验是为了保证信息在发送端和接收端之间传输的完整性,所以除了在收发两端都要实现CRC计算之外,还需要确定一些具体的机制,主要的几种机制分类列举如下:

表 1-1 收发端CRC校验的六种机制

|

机制 |

发送端 |

接收端 |

|||

|

初始寄存器值 |

校验序列 |

初始寄存器值 |

校验范围 |

正确判定 |

|

|

1 |

0 |

不操作 |

0 |

明文 |

结果=校验序列? |

|

2 |

0 |

不操作 |

0 |

明文+序列 |

结果=0? |

|

3 |

0 |

逐位取反 |

0 |

明文+序列 |

结果=Magic Num? |

|

4 |

全1 |

不操作 |

全1 |

明文 |

结果=校验序列? |

|

5 |

全1 |

不操作 |

全1 |

明文+序列 |

结果=0? |

|

6 |

全1 |

逐位取反 |

全1 |

明文+序列 |

结果=Magic Num? |

初始寄存器。初始寄存器的值为0,符合一般的CRC校验原理,也便于在MATLAB中计算。但是容易出现“前导0”问题,即在明文序列之前插入或者删除0序列,这是由于0与0异为0。因此,将初始寄存器值设为全1可以避免“前导0”的出现。发送端和接收端的初始寄存器值须保持一致以保证两端校验正确。

接收端的校验范围。可以选择明文或者明文+序列,若传输完整无误,明文的CRC计算结果等于收到的校验序列,明文+序列的计算结果归0。两者相比,后者实现流程简单。

Magic Num。明文+序列的计算结果归0并不定能严格证明信息传输完整无误,无法检测“拖尾0”问题,即在序列之后插入或者删除0序列,同样是由于0与0异为0。所以引入了Magic Num的机制,在发送端需要对校验序列逐位取反添加在明文序列之后发送,在接收端对明文+序列做校验,若结果等于Magic Num则说明信息传输完整无误。Magic Num是与生成多项式对应的序列,计算过程如下:

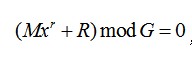

一般情况下,在接收端对明文+序列做计算,结果为0说明传输完整无误: ,其中M是明文序列,R是校验序列,G是生成多项式。

,其中M是明文序列,R是校验序列,G是生成多项式。

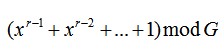

因此,由接收端计算出的无差错的传输的校验和应该是: ,这就是Magic Number。

,这就是Magic Number。

Magic Num的校验方法在网络传输的设计中比较常见,在802.3的IP核和802.11标准的附录框图中对CRC32校验的设计都采用了初始寄存器全1和Magic Num的方式。

参考资料:

http://blog.sina.com.cn/s/blog_62d9edac01015lsd.html

http://blog.csdn.net/highyyy/article/details/6208227

http://www.eefocus.com/Galois/blog/10-02/184555_16c21.html

http://wenku.baidu.com/view/a5b7d38002d276a200292e80

/2

/2

用户271389 2013-6-11 11:32

用户403664 2013-6-9 15:40