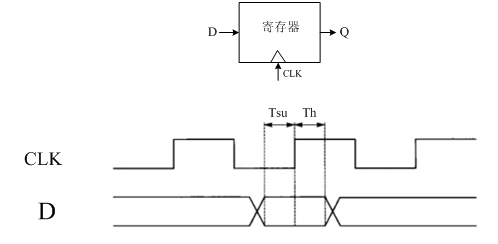

1、什么是建立时间(Tsu)和保持时间(Th)

以上升沿锁存为例,建立时间是指在时钟翻转之前输入的数据D必须保持稳定的时间;保持时间是在时钟翻转之后输入数据D必须保持稳定的时间[1]。如下图所示,一个数据要在上升沿被锁存,那么这个数据就要在时钟上升沿的建立时间和保持时间内保持稳定。

图1 建立时间和保持时间

建立时间与保持时间,是对触发器(或者寄存器)和锁存器而言,以能够稳定准确的锁存或者触发为目的,对其输入数据信号保持稳定的时间要求,具体数值与具体器件的内部结构特点密切相关,不能人为控制。建立时间和保持时间在时序分析中是一个很重要的准备知识,弄清楚这个两个时间对时序分析的原理的理解很有帮助。

2、根据内部结构分析建立时间和保持时间

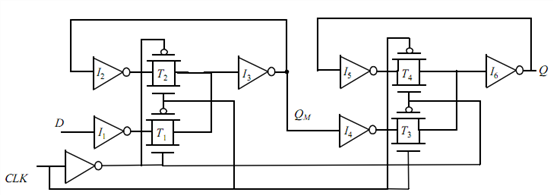

图2 经典的上升沿D触发器内部结构

关于为什么会有建立时间和保持时间,我曾试图从触发器或锁存器内部的结构去分析和证实,但是看了许多资料,由于触发器的内部结构有很多,所以分析方法很多,说法也很多。下面我选两个比较经典的结构来分析一下建立时间和保持时间。

以经典边沿触发的D触发器为例子,从内部结构上分析一下D触发器建立时间和保持时间。这个说明主要来源于EETOP的一篇帖子,其结构在维基百科的触发器词条可以得到验证。

如上图所示,这是一个上升沿触发的D触发器,需要注意的是,图中的6个与非门都是有延迟的,也就是在某一时刻输入组合逻辑的数据,在一段时间之后才能影响其输出,这是产生建立时间和保持时间要求的最根本原因。

首先,我们在假设所有的与非门的延迟为0,叙述一下这个触发器的整体工作流程。

当CLK=0时,与非门G3和G4的输出均为1,输出的1反馈到G1和G2作为输入,导致G1和G2的输出分别为D和/D,输出的D和/D又反馈到G3和G4;而G5和G6在此期间一直锁存着之前的数据,不受输入影响。

图3 CLK=0时触发器内部信号详情

当CLK=1时,与非门G3和G4的输出变为/D和D,输出到G5和G6作为输入,根据锁存器的原理,G5和G6最终会稳定的输出Q和/Q。

图4 CLK=1时触发器内部信号详情

然后我们把门电路的时延加上。设G2和G1 的延迟为T1,当CLK=0时,如果D在时钟跳变前的T(T<T1)时间才从d1更新为d2,那么G1和G2在时钟跳变时刻的输出值肯定是d1和/d1,而不是d2和/d2,进而影响到G3和G4的输出。如果要使得G1和G2的输出为d2和/d2,就必须要求D起码在时钟跳变之前的T1时间内维持d2稳定不变。这个T1就是建立时间Tsu。

当CLK=1时,G3和G4的延迟为T2,当CLK=1时,如果D在时钟跳变之后的T(T<T2)时间从d2更新为d3,由于G3和G4的输出在T的时间内还保持为1,所以D的更新会影响G2和G1的输出,进而影响G3和G4的输出,进而影响G5和G6的输出,造成输出Q和/Q不稳。

第二个例子是来自《数字集成电路——电路、系统和设计(第二版)》第7章的由多路开关构成的主从型正沿触发寄存器。

(to be continue)

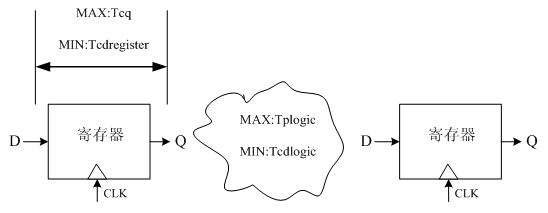

3、时序约束条件

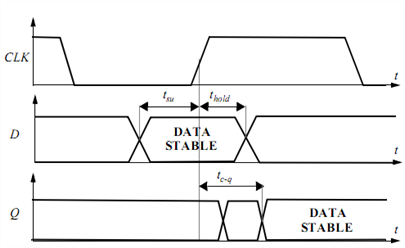

理解时序约束之前必须先理解几个时间间隔的概念和由来。

首先是建立时间Tsu和保持时间Th,之前已有具体介绍。

寄存器的最大传播延迟Tcq,是指时钟翻转之后,信号从寄存器的输入D到输出Q的最大延时;

寄存器的最小传播延迟Tcdregister,是指时钟翻转之后,信号从寄存器的输入D到输出Q的最小延时;

电路的线延迟和组合逻辑最大延迟Tplogic,是指本级寄存器的输出到下级寄存器的输入之间的电路最大延迟;

电路的线延迟和组合逻辑最小延迟Tcdlogic,是指本级寄存器的输出到下级寄存器的输入之间的电路最小延迟;

时钟周期T的必须能容纳寄存器的最大传播延时、电路的最大延迟以及建立时间的要求,所以有T >= Tcq + Tplogic + Tsu。

此外,为了保证时序元件的输入数据在时钟边沿之后能维持足够长的时间,而不会引入新数据而造成输入不稳,所以要求寄存器最小传播延迟和电路最小延时要大于寄存器的保持时间:即:Th <= Tcdregister + Tcdlogic。

参考文献:

[1].《深入浅出玩转FPGA》特权同学 北京航空航天大学出版社

[2].《数字集成电路——电路、系统和设计(第二版)》Jan M.Rabaey等著 周润德等译 电子工业出版社

[3].http://bbs.eetop.cn/viewthread.php?tid=308484&highlight=%BD%A8%C1%A2%CA%B1%BC%E4

[4].http://en.wikipedia.org/wiki/Flip-flop_(electronics)

/5

/5

文章评论(0条评论)

登录后参与讨论