软件部分EDS的几个版本没什么太多的不一样,所以这部分如果是新接触的同学,建议参考特权同学的书,或者是黑金社区的NIOSII那些事儿,都是不错的资料~

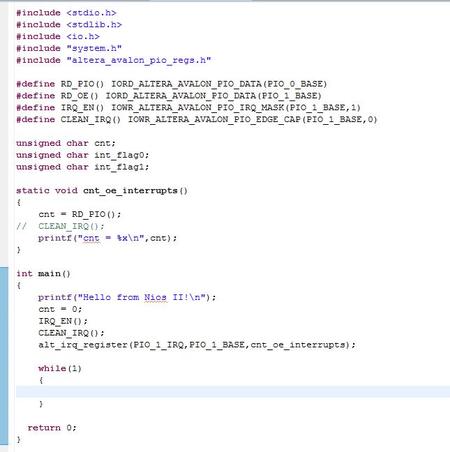

所以我就不班门弄斧了,附上代码截图:

其实代码方面最主要的就是一个中断服务程序,这部分设计相对灵活,可以完全根据被测信号的特点来处理。这也是比SignalTap优越的地方。

我们再来看看这样的方法可不可行。

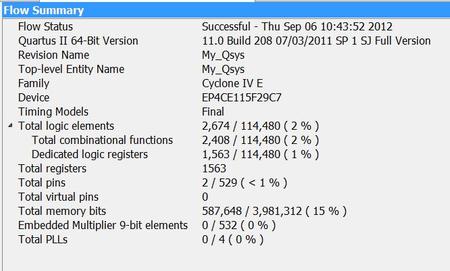

先看看我们的NIOS内核用了多少资源:

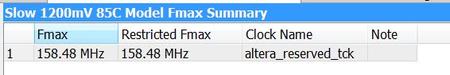

快速型的速度可达150M,就算是经济型也能到50M以上,所以,我们用它来处理一些并不是特别高速的数据是完全可行的。

另外我们再看看整个过程。选用SignalTap的话,需要新建一个SignalTap,然后添加采样时钟、被测信号量等,编译、烧写。如果重新分析,又要重新走一遍这样的流程。而且,当信号量增加时,SignalTap所占用的资源和存储器会随之线性增加,编译速度也随之更慢……还有一点,由于它作为附加电路加入到原设计中,还会对原设计造成一定的影响。

而如果使用NIOS内核,它完全可以独立开来单独设计,当信号量增加,随之增加的也就是PIO接口——这相对于FPGA来说,也就是内部的数据线!可以说是无穷无尽的。存储器也没有相应增加,依旧是搭建时的那个组件。最重要的一点,当我们把被监测信号量接入内核以后,编译Quartus,烧写到FPGA中后,就只需要在EDS中设计相应的监测软件程序就行了,不再需要编译、烧写,可以完全像在线调试单片机那样,既简单又快捷。

用户151427 2015-6-23 17:57

用户424825 2012-9-21 09:33

jlx_cuc 2012-9-17 08:20

用户957104 2012-9-14 18:36

821081701_371573822 2012-9-8 18:52