SignalTap在FPGA设计时常常作为在线调试工具来使用,但大家在使用它的时候都有一种感觉——这东西太慢,消耗太大的资源。慢,并不是说它跑得慢,而是每次修改参数变量就得重新编译一次,而编译就让我们感觉没操作一次就要花相当多的时间。另外,当我们需要监测很多个信号量时,需要消耗相当多的内部存储资源。

所以每次只有到了实在没办法的时候才愿意去选择SignalTap来查内部信号量……有时候真的很嫌弃它。在接触NiosII之后,发现这个东西还挺适合用来做一些监测工作的。

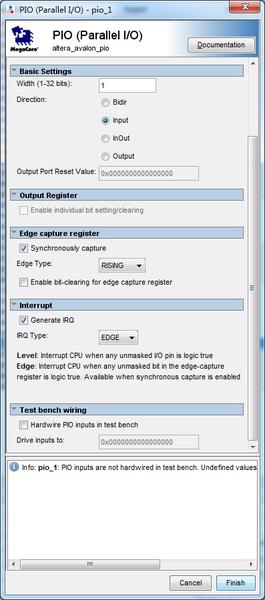

方案是:通过PIO将需监测的信号量接入到内核里,然后通过内部程序控制监测机制等,最后通过JTAG回传到EDS调试窗口。(其实就是用printf函数打印出来监测结果)

这样的好处在于:首先,Nios内核消耗资源不多,可能就是你算法设计里的边边角角就够了;再者,FPGA内部存储资源是有限的,但“内部”引脚可以说是无穷无尽的,所以不需要担心信号量太多而处理不过来。

下面用个寄存器累加值监测的小例子来简单说明下做法。

自QuartusII到10.1版本以后,便使用Qsys取代了SOPC Build,在此为方便还没怎么用过Qsys的朋友,稍微详细得介绍下。

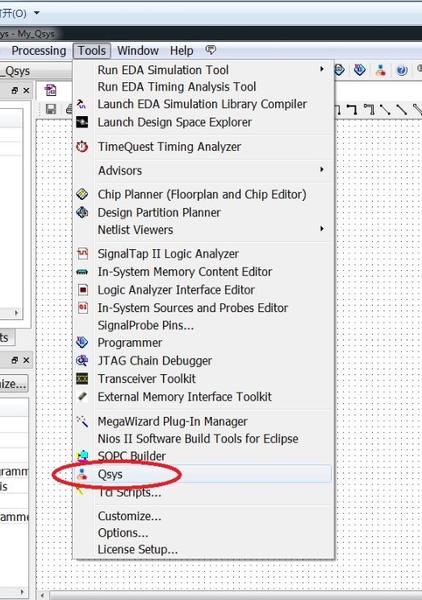

本人使用的是11.0版本,先建立个工程。然后可以在Tools里面找到Qsys选项,点击;

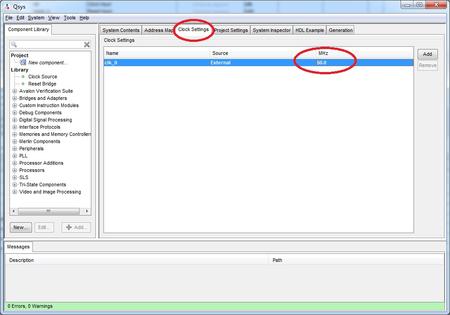

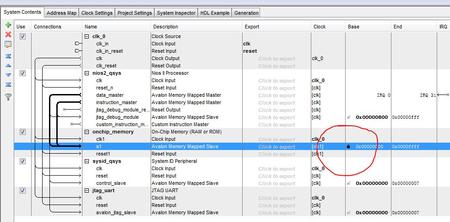

其中,初始便含有4个信号,两个时钟clk两个复位reset,这是和SOPC不一样的。然后可改变clk时钟频率参数,根据实验板上晶振或自己需求通过FPGA锁相环提供。

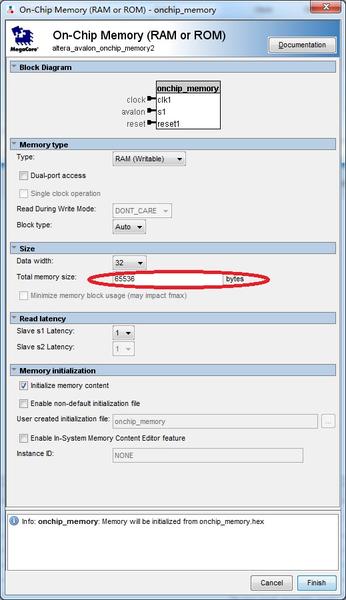

随后添加Nios内核,先不对其进行配置,待所有组件添加完后对其进行配置,按照默认参数添加后和SOPC中一样,需要进行重命名。再添加存储器,在这里我们使用FPGA嵌入式的目的是为了更方便地监测FPGA内部信号量,所以数据存储器和程序存储器我们都使用On-Chip Memory。大小可以不用很大,20k就够了,在本例中由于没有别的需要,选的大一些——64k。

添加完各个组件后,就需要我们手动地来连接他们了。其实很简单,时钟和复位接在初始产生的clk和clk_reset上,对于On-Chip Memory的s1需要连如两组数据总线上,其它的都只需接入内核的data_master。接好以后就可以重新配置我们的内核了:

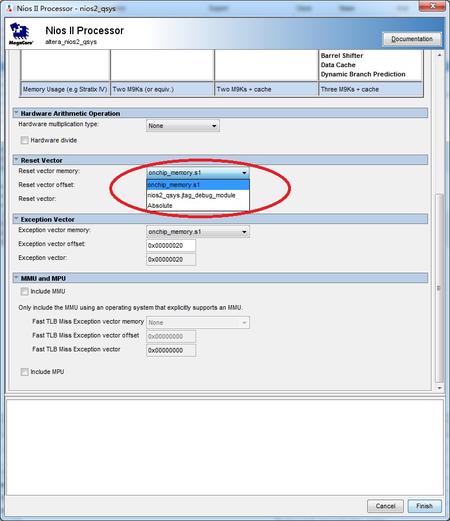

将两组memory都选为On-Chip Memory。内核选择NiosII/f,快速类型。

最后,锁定Memory地址后,自动分配地址:System->Assign Base Address。

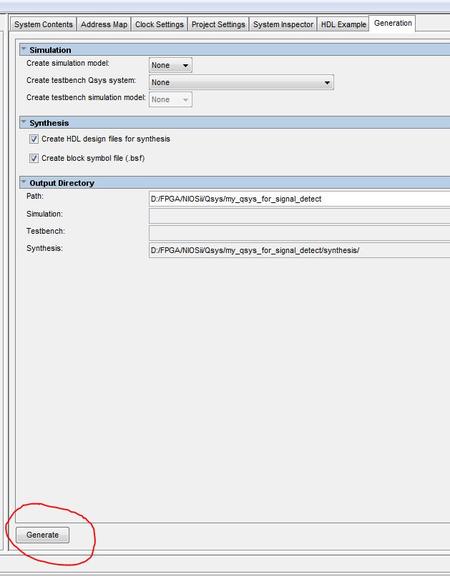

Generate以后就可以在顶层原理图中添加我们的内核了。

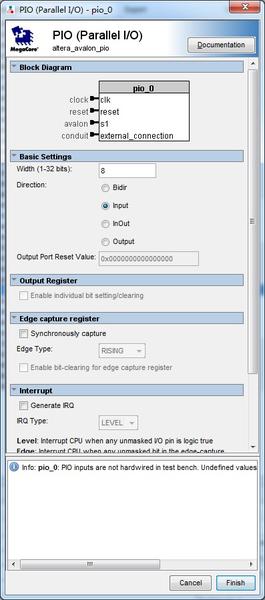

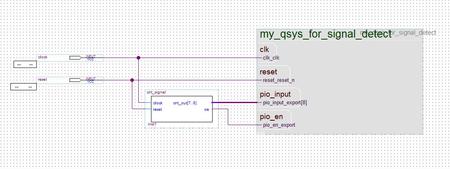

如下图,在顶层原理图设计时,将被监测模块的输出信号接入Nios的PIO口,这样FPGA部分的电路设计就完成了,之后只需要在EDS中设计相应的监测软件程序,再进行调试运行就可以实现我们对FPGA内部数据进行监测的功能了。

/2

/2

用户468778 2012-10-4 21:32

用户419124 2012-9-8 19:02