1.背景

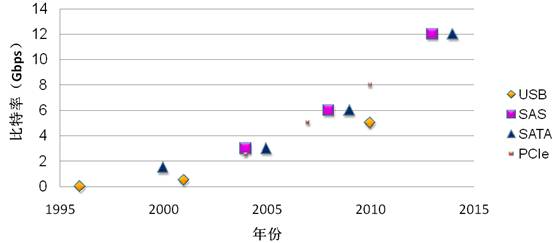

网络、多媒体、移动通信对提高数据吞吐率的需求与日俱增,推动计算机和通信技术不断突破速度极限。图 1是当前主流计算机外设总线的速率演变情况。

图 1 主流高速串行标准演进图

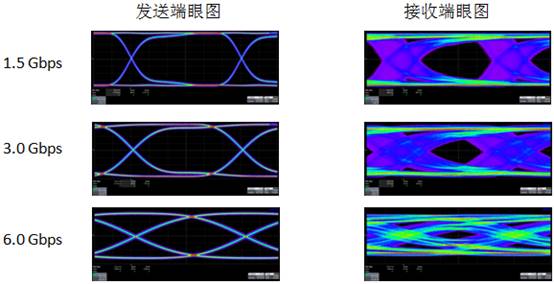

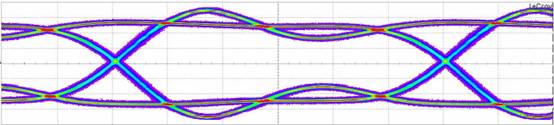

数据率越高,信道趋肤效应和介质损耗对信号质量的影响越严重,在时域上表现为:边沿变缓,码间干扰加剧,抖动增加。通常使用眼图来评估高速信号质量。下图是三种速率的信号在发送端和接收端分别测得的眼图。可以明显看出,速率越高,接收端的眼图闭合程度越小。能否在接收端正确检测出受损的信号,是高速收发器芯片设计者面临的挑战。

图 2 不同速率信号的失真程度

在以往的高速串行信号一致性测试标准里,一般都要求测试发送端性能,比如输出电压摆幅、上升时间、抖动、眼图等。随着速率提高,仅仅测试信号发送端已经不能保证高速链路能按预期性能正常工作,必须对接收机性能也进行测试。USB 3.0、PCI Express 3.0以及SATA和SAS规范已经明确要求进行接收机测试。

2.接收机测试原理

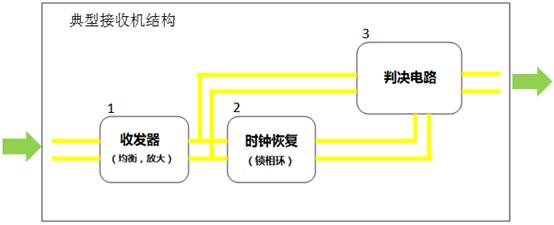

在发送器测试中,通常利用示波器直接测量输出信号的幅度、上升/下降时间、眼图和抖动,从而评估发送器的驱动能力、预加重、参考时钟稳定性等各项性能。在接收端,典型的接收机芯片框图如下:

图 3 典型接收机内部框图

它包含

信号检测(放大,均衡)

基于锁相环(PLL)的时钟恢复

判决电路(并转串,线路码解码)

对接收机性能的测试实际就是对以上三个主要部件的性能测试:

1)可以识别出多小幅度的信号,即接收灵敏度

2)时钟恢复电路中的锁相环能否去除低频抖动

3)能够正确识别出带有多大抖动的数据,即抖动容限

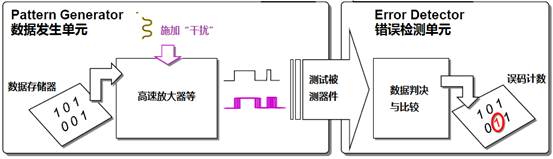

不像发送端可以直接测量被测件(Device Under Test,DUT)输出的信号,信号进入接收机内部后无法直接观测,一般使用仪器产生一定样本量、一定特征的激励数据流给DUT。这些特征一般是多种形式的“干扰”,仪器通过施加不同程度的“干扰”,测试接收机的表现。

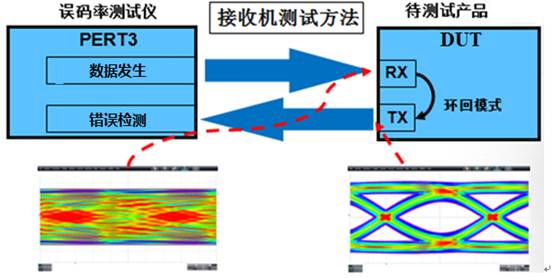

这种仪器一般是误码率测试仪(Bit Error Rate Tester,BERT)。简单的说,误码率测试就是发送已知数据给被测接收机芯片,通过量化被错误判决数据的比例来衡量接收机芯片的性能。在功能上,误码率测试仪包括数据发生(Pattern Gernerter)和错误检测(Error Detetor)两个部分,即前者产生激励,后者检测响应。

图 4 误码率测试仪工作原理框图

测试时,误码率测试仪和DUT收发互连形成回环,如图 5。Pattern Generator发出带有“干扰”的信号给DUT。DUT将接收到的数据经过内部回环又发送回给误码率测试仪。一般经过DUT内部的检测和时钟域变换,发送回去的数据不再带有“干扰”。

图 5 误码率测试仪与DUT回环连接

DUT一般有两种回环模式:

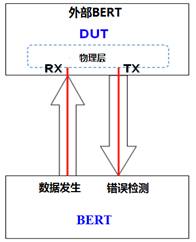

1)外部BERT(或称Retimed Loopback)

图 6 外部BERT测试框图

DUT将RX端收到的BERT数据从TX端发送回去,由BERT对比发送和接收到的数据

2)内部BERT

图 7 内部BERT测试框图

DUT直接对接收到的BERT数据进行误码判断,并把误码率测试结果保存在DUT寄存器里。BERT通过读取误码寄存器得到误码率测试结果。

如前文所述,误码率测试仪能够在激励信号中注入一定程度的“干扰”,并且“干扰”的特征参数可以定量调节,这些“干扰”包括:

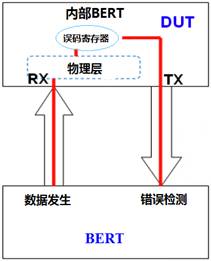

1)信号幅度

信号从发送器输出,经过信道到达接收端,幅度可能衰减以至于接收机无法识别。因此误码率测试仪通过逐步降低激励信号幅度,直到接收机芯片无法正确检测出数据,从而获得被测芯片的接收灵敏度。下图是一个典型的测试结果图,横坐标是激励信号的差模幅度,纵坐标代表共模偏置程度。绿色点表示接收机芯片能正常识别出该点代表的差模共模幅度,红叉则表示不能正常接收。这样能得一幅直观的接收机灵敏度图。

图 8 接收灵敏度测试结果图

2)预加重(Pre-Emphasis)

高速串行信号普遍运用预加重技术来补偿信道对信号高频分量的衰减。通过调节激励信号预加重程度可以补偿测试夹具、电缆的影响,确保信号达到接收端后的幅度符合预期。下图是一个预加重信号的眼图。

图 9 预加重后的信号眼图

3)抖动

接收机芯片中的时钟恢复电路运用锁相环来跟踪数据的跳变沿,其频响是一个低通滤波器。当串行数据信号的抖动变化频率较低时,处于直流到锁相环截至频率范围以内,锁相环就能及时追踪到数据跳变沿(即锁住相位),输出的时钟与输入数据同相(严格讲相位差为固定常数),这样抖动为零。当连续边沿的抖动变化太快时(即存在高频抖动时),锁相环不能及时追踪到边沿的变化,于是输出的时钟和数据边沿存在抖动。误码率测试仪可以输出含有定量正弦抖动(即周期抖动)和随机抖动的数据,从而评估接收机芯片的抖动容限。

图 10 含有周期抖动的激励信号眼图

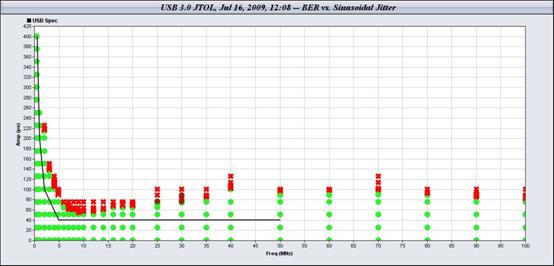

图 11是一个抖动容限测试结果图,横坐标表示抖动的频率,纵坐标表示抖动的值。绿色点表示在相应抖动激励下,接收机的误码率测试可以通过(例如小于10-12),红叉表示不能通过。图中一条黑色的曲线是USB3.0规范要求的抖动容限曲线。测试后,通过检查曲线下方是否有测试不通过点来判断接收机特性是否符合标准。

图 11 抖动容限测试结果图

4)时钟扩频(Spread Spectrum Clocking,SSC)

时钟扩频是用一个低频信号去调制时钟。在频谱上,时钟单一的谱线在调制后变为在一定范围内分布,从而降低频谱峰值水平。这是一种减小辐射发射峰值的方法。目前高速串行标准一般都要求支持时钟扩频,因此测试接收机能否识别出带有扩频的数据也是重要的测试内容。

3.力科接收机测试方案-PeRT3

PeRT3是Protocol-enabled Receiver and Transmitter Tolerance Tester的简写,即具备协议使能的接收机和发送器容限测试仪。包含Eagle和Phoenix两个系列,外观如下图:

图 12 力科PeRT3

PeRT3首先具备了BERT的Pattern Generator和Error Detector功能,可以对激励数据注入前文所提到的各种“干扰”,其次还具备业界其他BERT所不具有的功能:

1) 支持USB3.0,PCI Express,SATA,SAS标准规定的接收机一致性测试。目前是SuperSpeed USB (USB3.0)Platform Interoperability Lab采用和推荐的测试方案。

2) 能够自动完成协议握手和DUT的初始化。

3) 能够自动控制DUT进入或退出回环模式。如果没有这项功能,测试人员只能通过对DUT相关寄存器进行编程的方法使其进入特定状态,操作不方便。

1) USB3.0收发器为补偿发送和接收时钟的频率偏差,会在发送出去的码流中加入一些SKP符号。这样BERT的Error Detector将会收到测试码和多余的SKP符号。传统的BERT会误认为测量到了误码。而力科PeRT3可以智能地添加和删除SKP后,再来计算是否有误码。

2) 支持PCI Express Gen3动态均衡(Dynamic Equalization)测试

3) 除了可以测量误比特率,还可以测量误帧率(Frame Error Rate),识别和记录协议层的错误。

如果配合示波器使用,PeRT3能够完成发送器和接收机的全面测试,芯片设计者凭借这些测试验证工具,可对其高速收发器的设计充满信心。

参考文献

[1] David Li . Receiver Testing Basic. LeCroy Corporation.

[2] PeRT3 Eagle System User Manual. LeCroy Corporation.

作者简介

万力劢,应用工程师,美国力科公司成都代表处,成都市顺城大街308号冠城广场33层C座。028-86527180-106,limai.wan@lecroy.com

/4

/4

文章评论(0条评论)

登录后参与讨论