作者:John Betten,TI应用工程师

单端初级电感转换器(SEPIC)能够通过一个大于或者小于调节输出电压的输入电压工作。除能够起到一个降压及升压转换器的作用以外,SEPIC还具有最少的有源组件、一个简易控制器和钳位开关波形,从而提供低噪声运行。看是否使用两个磁绕组,是我们识别SEPIC的一般方法。这些绕组可绕于共用铁芯上,其与耦合双绕组电感的情况一样,或者它们也可以是两个非耦合电感的单独绕组。设计人员通常不确定哪一种方法最佳,以及两种方法之间是否存在实际差异。本文对每种方法进行研究,并讨论每种方法对实际SEPIC设计产生的影响。

电路运行

图 1 显示了耦合电感的基本SEPIC。当FET(Q1)开启时,输入电压施加于初级绕组。由于绕组比为1:1,因此次级绕组也被施加了一个与输入电压相等的电压;但是,由于绕组的极性,整流器(D1)的阳极被拉负,并被反向偏置。整流器偏颇关闭,要求输出电容在这种“导通”时间期间支持负载,从而强迫AC电容(CAC) 充电至输入电压。Q1开启时,两个绕组的电流为Q1到接地,而次级电流流经AC电容。“导通”时间期间总FET电流为输入电流和输出次级电流的和。

FET关闭时,绕组的电压反向极性,以维持电流。整流器导电向输出端提供电流时,次级绕组电压现在被钳位至输出电压。通过变压器作用,它对初级绕组的输出电压进行钳位。FET的漏极电压被钳位至输入电压加输出电压。FET“关闭”时间期间,两个绕组的电流流经D1至输出端,而初级电流则流经AC电容。

伏-微秒平衡

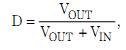

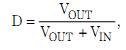

耦合电感由两个非耦合电感代替时,电路运行情况类似。要让电路正确运行,必须在每个磁芯之间维持伏-微秒平衡。也就是说,对于两个非耦合电感而言,在FET“导通”和“关闭”时间期间,每个电感电压和时间的积必须大小相等,而极性相反。通过代数方法表明,非耦合电感的AC电容电压也被充电至输入电压。在FET“关闭”时间期间,输出端电感被钳位至输出电压,其与耦合电感的次级绕组一样。在 FET“导通”时间期间,AC电容在电感施加一个与输入电压相等但极性相反的电势。每间隔时间,对电感定义电压进行钳位,这样伏-微秒平衡便决定了占空比(D)的大小。其在连续导通模式(CCM)运行时,可简单表示为:

FET导通时,施加于输入端电感的电压等于输入电压。FET关闭时,伏-微秒平衡通过钳位其 VOUT 来维持。记住,FET导通时,输入电压施加于两个电感;FET关闭时,输出电压施加于两个电感。两个非耦合电感SEPIC的电压和电流波形,与耦合电感版本的情况非常类似,以至于很难分辨它们。

两个还是一个?

如果SEPIC类型之间确实存在少许的电路运行差异的话,那么我们应该使用哪一种呢?我们通常选择使用耦合电感,是因其更少的组件数目、更佳的集成度以及相对于使用两个单电感而言更低的电感要求。然而,高功率现货耦合电感有限的选择范围,成为摆在广大电源设计人员面前的一个难题。如果他们选择设计其自己的电感,则必须规定所有相关电参数,并且必须面对更长的交货时间问题。耦合电感SEPIC可受益于漏电感,其可降低AC电流损耗。耦合电感必须具有1:1的匝数比,以实施伏-微秒平衡。选择使用两个单独的非耦合电感,一般可以更广泛地选择许多现货组件。由于并不要求每个电感的电流和电感完全相等,因此可以选择使用不同的组件尺寸,从而带来更大的灵活性。

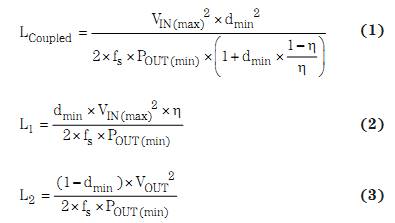

方程式1到3表明了耦合电感和非耦合电感的电感计算过程。

方程式计算得到最大输入电压和最小负载时 CCM 运行所需的最小电感。50%占空比运行(VIN等于VOUT时出现)和统一效率条件下,比较这些方程式可知,方程式 1 中耦合电感的计算值是非耦合电感计算值的两倍。由于转换器肯定会有损耗,而大多数输入电压源均有很大不同,因此这种简化了的电感泛化一般为错误的;但它通常足以应付除极端情况以外的所有情况。它一般意味着,转换器会比预期稍快一点进入非连续导通模式 (DCM) 运行,其在大多数情况下仍然可以接受。如前所述,使用非耦合电感时,正如我们通常假设的那样,无需输出端电感的值与输入端电感一样;但是为了简单起见肯定会这样做。利用VOUT/VIN调节输入端电感,便可确定输出端电感值。使用更小值输出端电感的好处是,它一般尺寸更小而且成本更低。

实例设计

“表1”所示规范为设计比较的基础。第一个设计使用一个耦合电感,而第二个则使用两个非耦合电感。

使用一个耦合电感的设计是典型的64W输出功率车载输入电压范围。方程式1表明,耦合电感要求12µH的电感,以及13A的组合电流额定值(基于 IIN + IOUT)。这种设计特别具有挑战性,因为现货电感选择范围有限。因此,我们指定并设计了Renco自定义电感。该电感缠绕在一个分离式线轴上以产生漏电感,旨在最小化能够引起损耗的循环AC电流。产生这些损耗的因为,施加在漏电感的AC电容纹波电压。若想实施低功耗设计,Coilcraft(MSS1278系列)和Coiltronics(DRQ74/127系列)的耦合电感均是较好的现货产品。

就非耦合电感设计而言,33-µH Coilcraft SER2918用于L1,而22-µH Coiltronics HC9 则用于 L2。它们的选择均基于绕组电阻、额定电流和尺寸。选择电感时,设计人员必须注意还要考虑铁芯和AC绕组损耗。这些损耗可降低电感的有效DC电流,但并非所有厂商都提供计算所需的全部信息。错误的计算结果,会大大增加铁芯温度,使其超出典型的40°C温升。它还会降低效率,并且加速过早失效现象的出现。

表1原型SEPIC电气规范

|

参数

|

规范

|

|

输入电压

|

8到32V

|

|

输出电压

|

16V

|

|

最大输出电流

|

4A

|

|

纹波

|

1%

|

|

最小效率(最大负载)

|

91%

|

图2使用耦合电感的SEPIC(4A时16V)

图2显示了使用一个耦合电感的原型SEPIC的示意图。若想在设计中实施非耦合电感,只需在相同PWB上用两个电感替换耦合电感便可。图3显示了两种原型电路。图3b中,L1占用了耦合电感的空间,而L2则位于右上角。

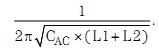

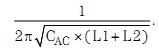

正如预计的那样,两个电路以一种近乎完全一样的方式工作,且开关电压和电流波形实质相同。但在性能方面存在一些重要的差异。耦合电感设计的控制环路相当良性,而非耦合电感设计则在最初时候出现不稳定。环路增益测量表明,高Q、低频谐振是罪魁祸首,其要求添加一个R/C阻尼滤波器与AC电容并联。极大简化时,谐振频率似乎约为:

图3SEPIC

SEPIC电路具有非常复杂的控制环路特性,同时由于分析结果的解释一般较为困难,因此必需使用一些数学工具来进行具体分析。添加这种R/C阻尼滤波器(220 µF/2Ω)会增加成本、电路面积和损耗。相比一个单耦合电感,使用两个非耦合电感会使面积增加10%。

图 4 显示了两种电路的测量效率。我们可以看到,耦合电感设计的效率增加多达0.5%。这可能是由于耦合电感设计的总铁芯损耗更低,因为其DC接线损耗实际高于使用非耦合电感的设计。L2使用一种粉状铁芯材料,其往往具有比L1和自定义Renco耦合电感所用铁氧体材料更高的损耗。尽管使用了L2的铁氧体材料,但其会导致更大的面积。

结论

利用一个耦合电感或者两个非耦合电感,均能成功实施SEPIC。更高的效率、更小的电路面积以及更良性的控制环路特性,这些都是使用正确缠绕的自定义耦合电感时原型硬件所带来的好处。自定义组件没有现货器件那么理想,而许多耦合电感随处可以购买到,且尺寸更小。如果产品上市场时间至关重要,则非耦合电感可为设计人员带来更大的灵活性。

图 4 耦合和非耦合电感均获得了较好的效率

/3

/3

文章评论(0条评论)

登录后参与讨论