作者:Hello,Panda

1.目标

配置CMOS Sensor OV9734,并通过MIPI DPHY硬核接收数据。

(1)使用一个RISC-V软核,实通过AHB总线访问I2C FIFO,通过I2C总线配置OV9734 Sensor;

(2)使用MIPI DPHY硬核接收图像数据,并实现CSI层恢复成为图像像素。

(3)OV9734配置为连续时钟模式,单Lane,数据率360Mbps,1280*720P,30fps。

2.软件设计

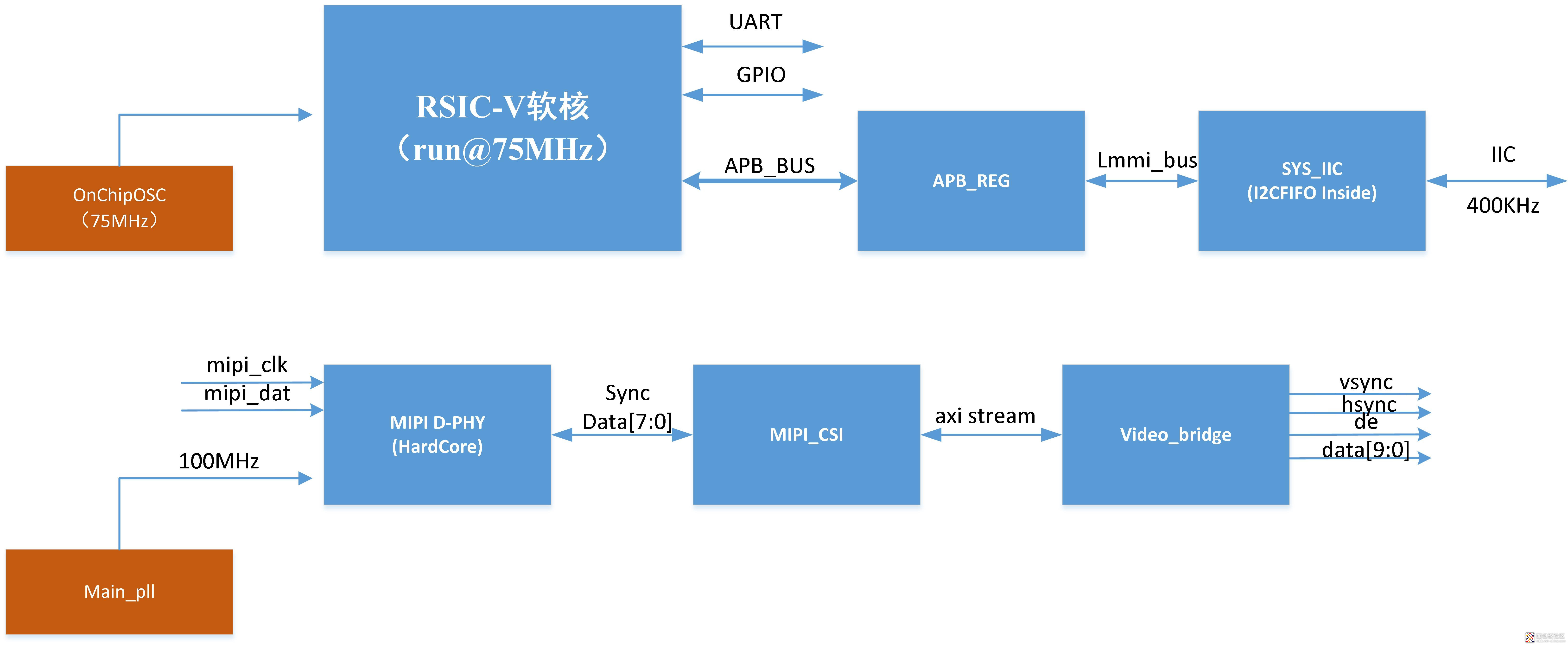

本例涉及到使用RISC-V软核,MIPI DPHY硬核,I2C FIFO和MIPI CSI解析层等。软件架构如下图1所示。

图1 FPGA软件总体框图

2.1 RISC-V软核

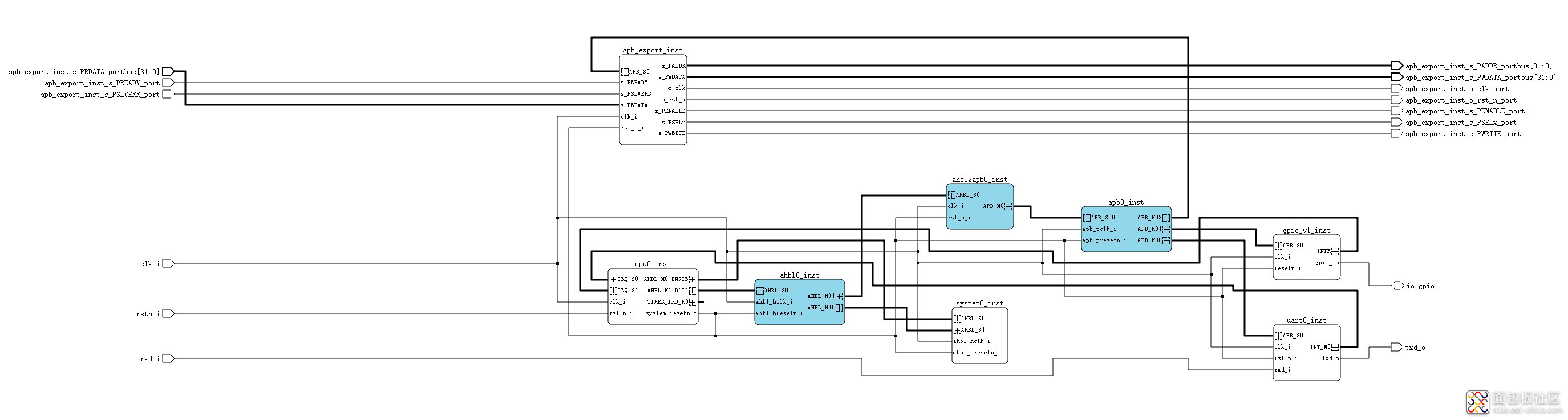

软核在propel Builder开发环境中进行例化和配置,如下图2所示,例化了RISC-V软核、本地32KB运行RAM、Ahb2Apb桥、Apb interconnect、GPIO和UART等基础IP,另外自定义一个Apb export IP用于给引出到外部的APB总线分配地址。

图2 RISC-V软核配置

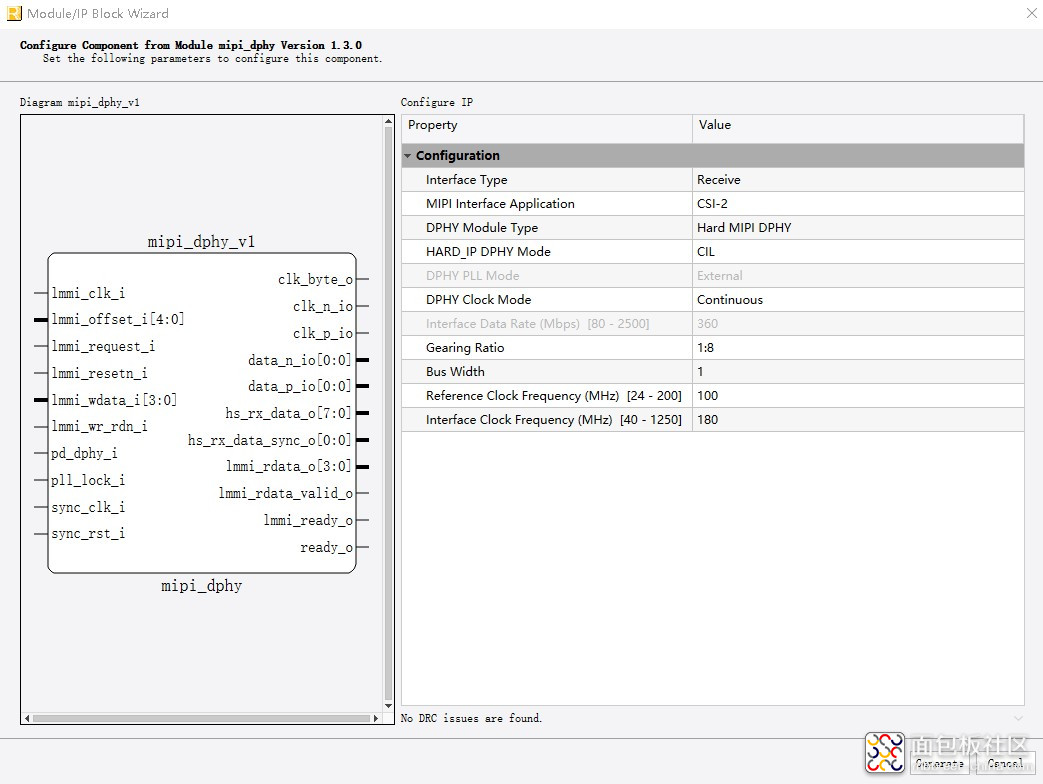

2.2 MIPI DPHY硬核

Crosslink-NX器件有两个2.5Gbps lane速率的MIPI D-PHY硬核。使用硬核IP MIPI_DPHY(V1.3.0)模组进行例化(注:在Radiant中,不同版本的IP端口相差很大),例化参数如下图3。

图3 例化参数

在本例中,结合OV9734的配置,接口时钟为180MHz,Lane(bus width)数为1,时钟模式为continuous,Gearing Ratio为1:8,模式为包括控制模块CIL。

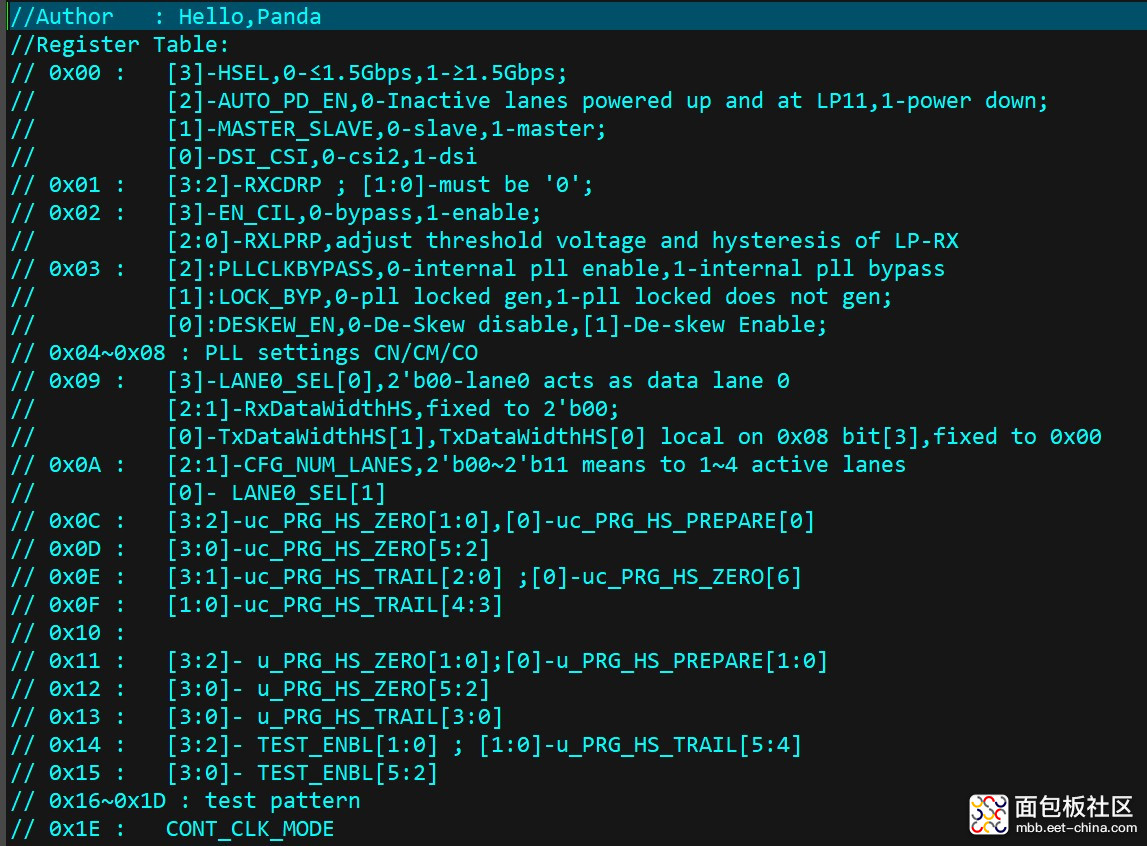

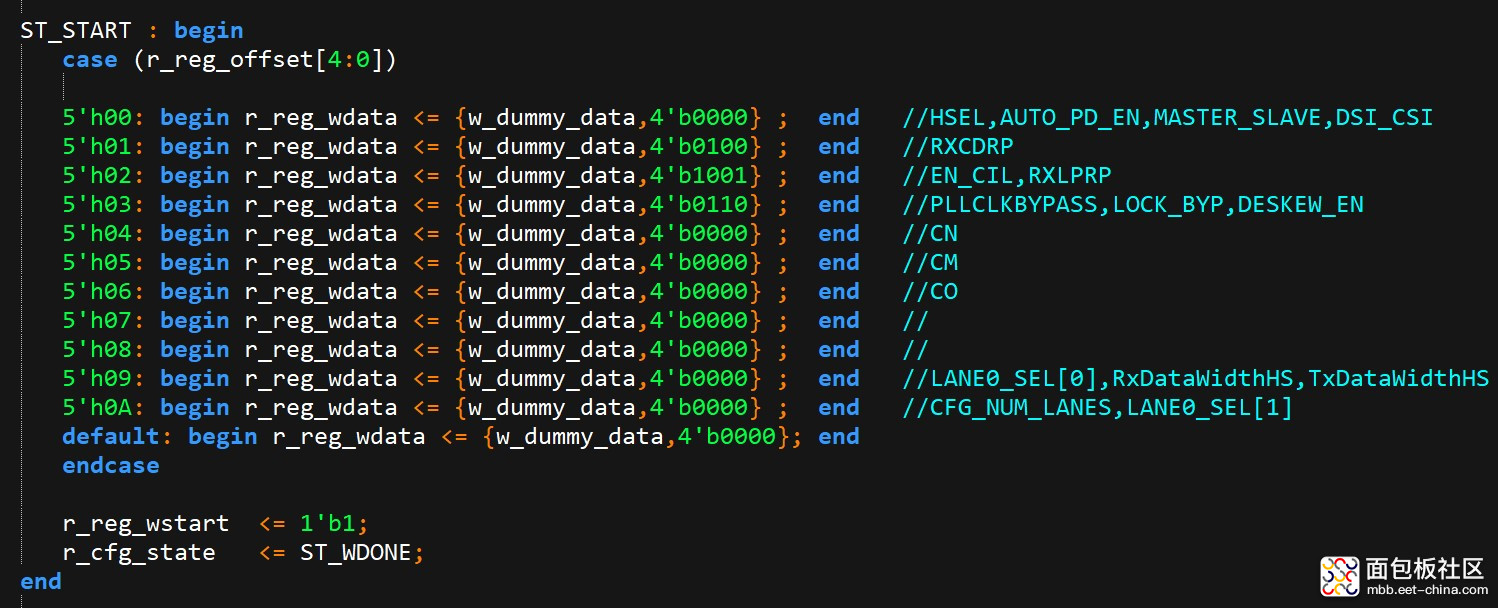

MIPI硬核在使用前需通过lmmi总线对其内部寄存器进行配置,配置寄存器空间见下图4,详细的寄存器描述请参考官方数据手册,lattice文档编号为:FPGA-IPUG-02061-1.5。

图4 寄存器地址空间

针对本例的D-PHY接口参数,配置值见下图5(请特别注意,虽然在IP生成器里面进行了参数例化,还必须通过lmmi总线向寄存器控制配置正确的值硬核才可正常工作)。

图5 本例寄存器空间配置值

按照之前相关连载文章的示例,编译和在线下载bit文件,运行Lattice Propel下的RISC-V软核C代码配置好OV9734,系统即可正常采集到MIPI输出的图像数据,如下图6所示。

图6 在线调试抓取到的D-PHY硬核输出数据

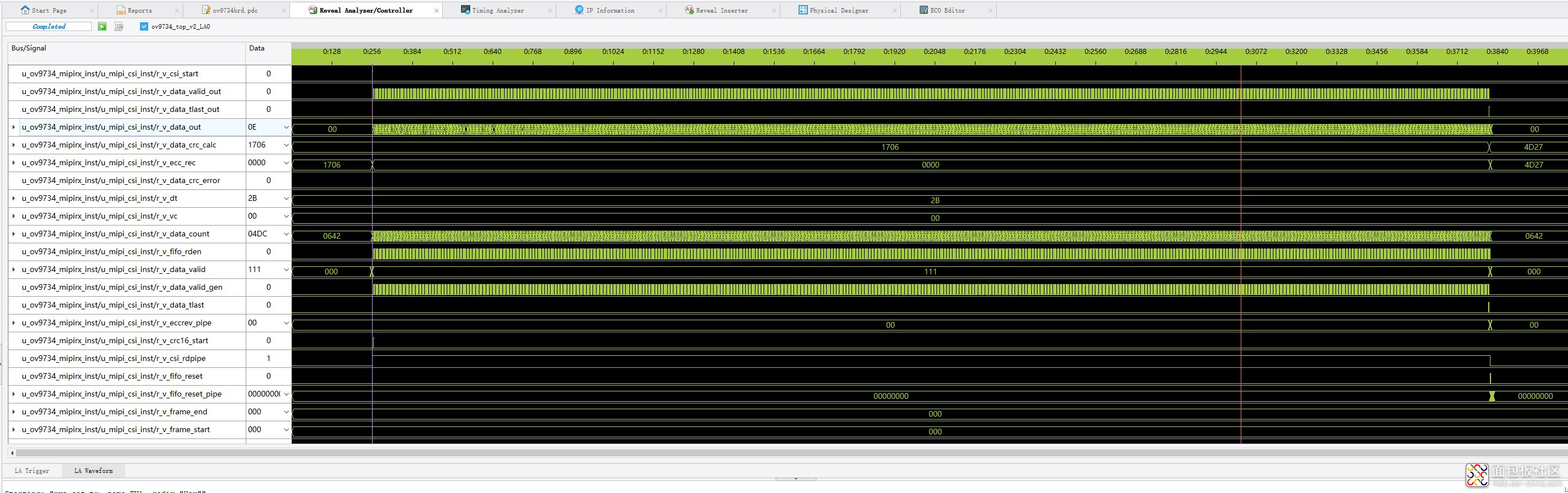

2.3 CSI层

Lattice Radiant开发环境中提供了官方IP,CSI-2/DSI D-PHY Receiver这个IP,内容很全面,但是需要购买付费授权,以熊猫君羞涩的口袋,自然是购买不起,咱只能自己手撸一个针对本例的CSI解析代码,说实在的,做一个能稳定针对特定格式的代码,解析帧头,做一个帧头效验和数据效验,并将其转化为stream格式输出,不难,一会儿就做好了。下图7是在线调试抓取到的CSI-2解析后的数据。

图7 在线调试抓取到的CSI-2层解析后的数据

2.4 Video Bridge

该模块将来自CSI层数据按照DT指定的格式拼接并生成标准的视频时序。后端即可接入通用的ISP处理模块进行进一步的算法运算处理。下图8是接收OV9734的MIPI数据后直接显示的RAW照片。

图8 显示RAW照片

3.结语

因Crosslink-NX集成了2.5Gbps Lane速率的MIPI硬核,因此开发变得像通用处理器一样简单,只要认真阅读手册,很快就能上手出图。另外,针对特定DT格式的CSI层的协议解析也很容易,可以不依赖官方的付费IP,对熟悉的同学们而言,几乎就是一日之功而已。最后,欢迎搭建加入QQ讨论群或关注“ZYNQ分享客”微信公众号,共同讨论进步!

/5

/5

文章评论(0条评论)

登录后参与讨论