作者:Hello,Panda

前一阵子,熊猫君开发了一套Sony SLVS-EC的图像传感器接口数据接收IP,最近稍微闲了一些,码一点字儿分享一下。

SLVS-EC是Sony推出的接口标准,目前版本已经发展到v2.0,是他们家的一个私有标准,主要是为了满足大靶面、高速图像传感器对大带宽的要求,在V2.0版本下,单lane的带宽已经到了约4.752Gbps,这里说的“约”,是因为标准对速率并没有强制规定,不同型号的Sensor速率上可能会有一些小的差别。由于现在Sony的图像传感器靶面越来越大,100M像素以上的也很多;帧率也越来越高,1000fps以上的也不在少数,因此SLVS-EC接口在至少在Sony的Sensor上会用得越来越多。

这篇分享分为两部分,第一部分为“SLVS-EC标准解读”,第二部分为“SLVS-EC接口FPGA实现”。

第一部分:SLVS-EC标准简要解读

1.1 电气特性

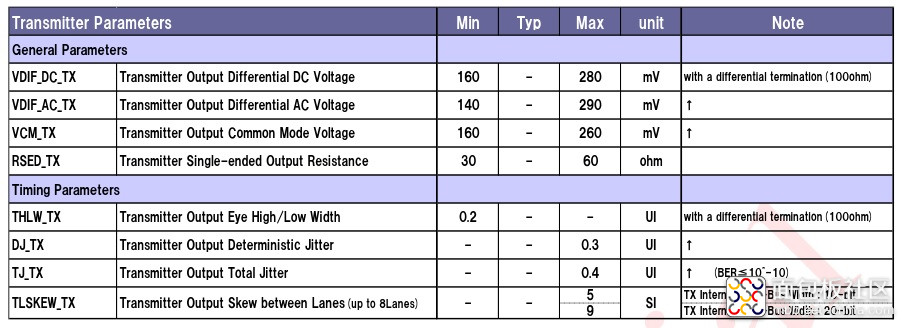

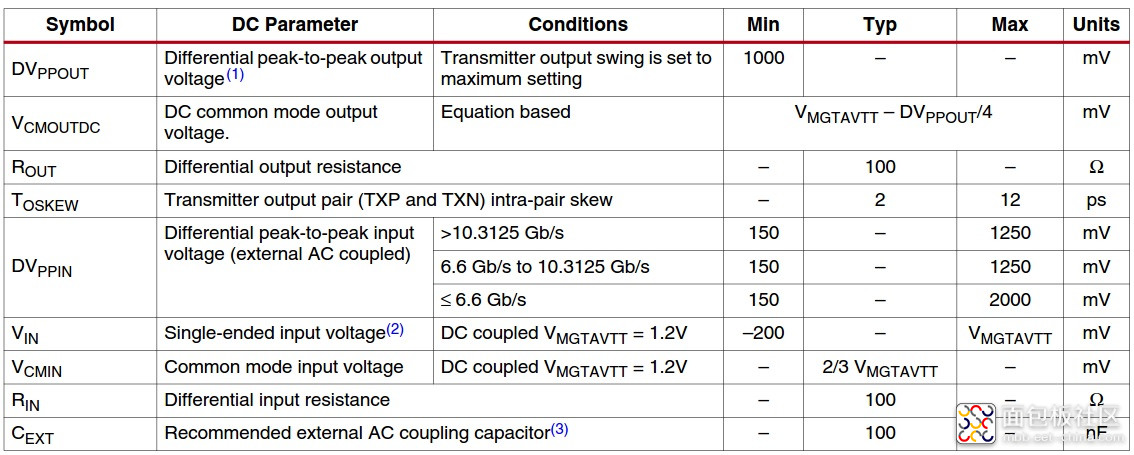

首先我们读它的电气特性,SLVS-EC的电气特性见下表1,它的发送端差分摆幅是140mV~290mV。一般情况下,Xilinx K7系列FPGA的高速Serdes GTX可接收的差分摆幅范围AC耦合下为150mV~1250mV,如图2所示。

因此,并不是所有的FPGA都可以接收极端条件下的SLVS-EC电平,所以,在确定系统方案之前,需要仔细阅读电平是否匹配,一般的sensor里面可能会有寄存器可以调节差分输出的摆幅或者其最小输出摆幅比标准里面的要高一些。

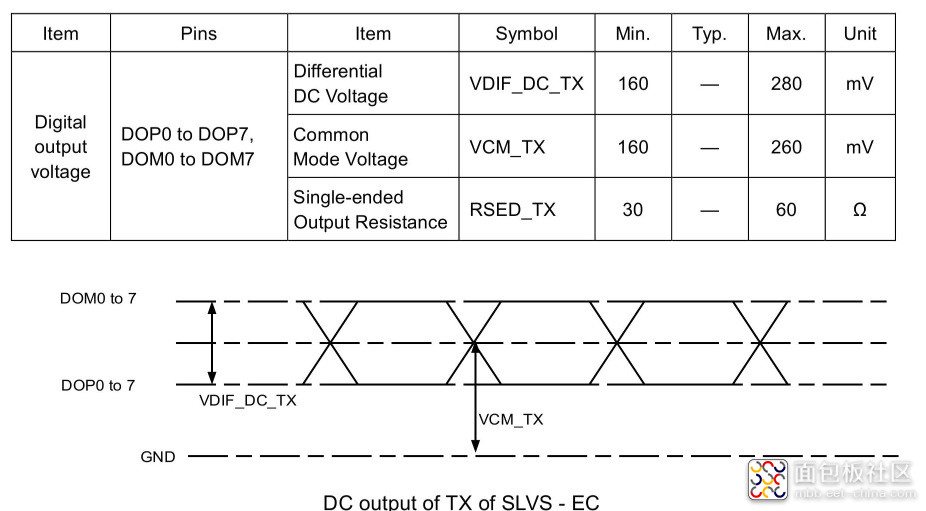

那么,我们找一颗Sensor,看看实际情况如何。如下图3所示是Sony IMX421的SLVS-EC输出特性,从图中可知,其差分摆幅是160mV~280mV,在xilinx K7

FPGA的接收范围之内,可以用K7系列的FPGA来接收。

到这里,我们知道SLVS-EC对接收主控的电气特性有一定要求,需要匹配才行。

图1 SLVS-EC TX端电气特性

图2 Xilinx K7系列FPGA GTX电气特性

图3 IMX421 输出电气特性

1.2 通道和编码

然后我们再看它支持的数据通道形式和所支持的编码格式。

1.2.1 SLVS-EC通道结构

SLVS-EC是一个单项高速数据接口,也就是说它的传输方向只能是从TX端到RX端,并没有反馈传输的功能。一般的,单个TX物理层支持的最大Lane数是8Lane,如果超过8 Lane,则使用多个物理层并行传输。配置、控制和状态数据通过IIC接口反馈。

1.2.2 编码格式

SLVS-EC接口使用常规的8B/10B编码,使用符号K28.5作为对齐码。

1.3 工作模式

和所有其他的Sony Sensor一样,SLVS-EC接口的Sensor可工作在主控Master模式和Sensor Master模式,区别是前者由主控产生XVS、XHS同步信号;后者由Sensor产生XVS和XHS信号。

Sensor的输入时钟可由Sensor板本地提供或由主控端提供。

和MIPI CSI的分层类似,SLVS-EC接口由上而下分为应用层、链路层和物理层。各个层级的分工如下:

1.2.1 应用层

(1)按格式生成RAW数据;

(2)按格式生成Embedded数据;

(3)按格式产生数据帧;

(4)应用系统控制协议;

(5)产生帧同步、行同步数据;

(6)配置和应用SLVS-EC接口相关的寄存器(来自IIC);

(7)相机控制接口通信(IIC)。

1.2.2 链路层

(1)将像素数据进行格式转换为字节数据;

(2)负载数据错误校正(选配);

(3)封装和插入数据包头;

(4)帧尾负载数据错误检测(选配);

(5)Lane管理;

(6)配置管理和产生帧头、帧尾。

1.2.3 物理层

(1)PHY协议控制码的产生和提取;

(2)带宽控制;

(3)skew控制;

(4)Comma符号对齐;

(5)符号编解码;

(6)串行化和去串行化;

(6)时钟产生和恢复;

(7)SLVS-EC信号的传输和路由。

1.4 应用层协议

SLVS-EC接口支持RAW8/RAW10/RAW12/RAW14/RAW16数据格式,对于每个Lane而言,传输的像素数必须是4的整数倍。

SLVS-EC接口可以传输“Embedded Data”,用于传输自定义数据、寄存器值等等这些,在标准里面并未对“Embedded Data”的具体内容和格式进行定义。和像素数据不同的是,此类数据不能从发送错误中恢复,接收端通过帧尾效验确认接收数据是否出错,出错只能丢掉。

1.4.1 帧格式

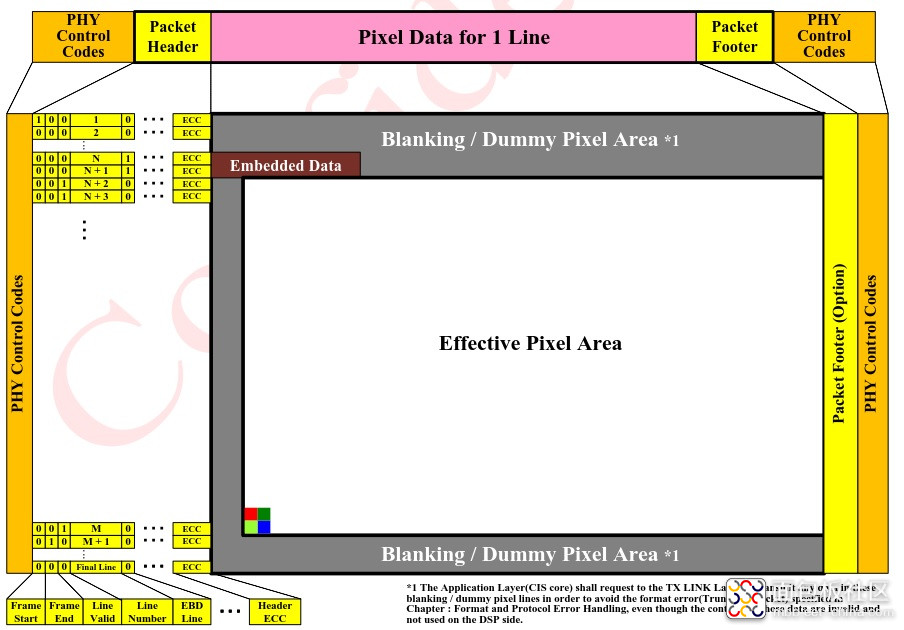

SLVS-EC支持“单流传输”和“多流传输”两种帧模式,多流模式下,多组SLVS-EC流可以传输不同的内容。下图4是一组流传输的格式,跟通用的LVDS图像格式一样,数据包发送以行为单位,包括Blank行、Embedded Data行、有效数据行等,每行有效数据包括帧头、帧尾和数据载荷。

图4 单流传输帧格式

数据帧在传输的过程支持模式切换,切换的模式在下一帧开始时生效,模式切换以后接收端需要重新进行初始化流程。模式切换支持中断,配置好寄存器后,由主控给Sensor一个中断信号,新的一帧在收到中断信后强制开始。

1.4.2 寄存器

SLVS-EC寄存器有接口属性寄存器和配置寄存器两种,通过IIC进行设置,前者主要配置物理层的一些电气参数,后者主要配置通道数、像素位等参数,一般的,这些参数在图像传感器中会根据Sensor参数自动设置为特定值,有极少数的可能需要用户通过IIC进行初始化配置。

1.5 链路层协议

链路层最主要的工作就是数据封包。

1.5.1 像素到字节的格式转换

跟MIPI CSI-2协议类似,SLVS-EC的基本数据传输单位也是字节,就需要将RAW8/10/12/14/16像素转换为字节再进行传输,这里在恢复数据时仔细对照标准中的描述即可,也是最为重要的内容。

1.5.2 载荷数据

数据载荷的字节数需是16的整数倍,不足的字节必须填充为全零。

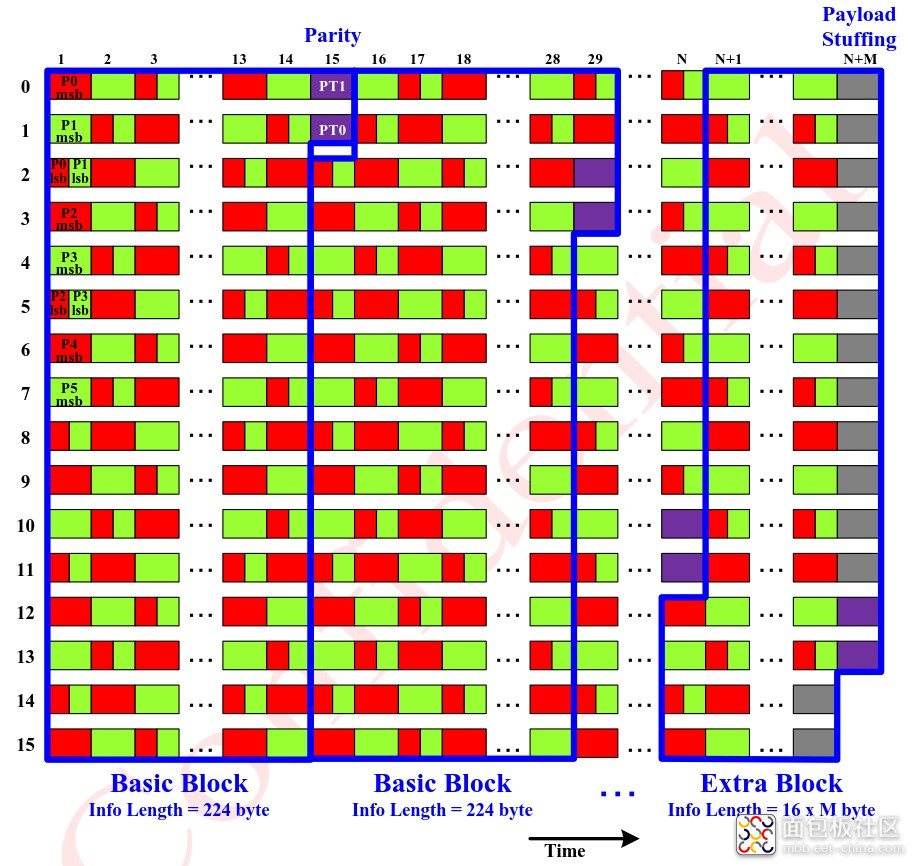

数据载荷支持ECC效验,也可以配置为不支持ECC,因此有三种模式,分别是不支持ECC-0、ECC-1和ECC-2,为了便于描述,咱们把一个数据包又分为若干个数据块,每个数据块有效数据最多为224字节,最少为16字节。那么,在ECC-1模式时,每个块插入2字节的ECC多项式,此时一个数据块为18~226字节;在ECC-2模式时,需要插入4个字节的ECC多项式,此时一个数据块为20~228字节。效验字高字节在前。

在一个数据包里面,将每个整的数据块称之为“Basic Block”,一个数据包的结尾不足整数块字节数的块称之为“Extra Block”,如下图5所示是ECC-1模式下的块结构图,图中TP1为多项式的高字节,PT0为多项式的低字节。

ECC多项式的生成和计算参照标准文档计算即可。

图5 ECC-Option1时的数据块结构图

1.5.3封包

封包就是在数据的基础上加上包头(packet headr)和包尾(packet footer)。包尾就是CRC效验,可以通过寄存器设置是否应用CRC效验特性。需要特别注意的是,packet footer,也就是CRC特性和数据载荷ECC特性是互斥的,二者只可使用一种。

接收端恢复数据并检测到错误后,按照标准所述的错误处理方法进行处理。

1.5.4 通道管理

SLVS-EC接口允许配置为1、2、4、6、8通道,未使用通道为高阻态。在实际传输过程中,每个lane传输的字节数需为一致,字节数不是lane数量的整数倍时,需补齐填充0。

在关闭CRC时,Footer的长度为0;当CRC使能时,Footer的长度为4字节。在使能ECC功能时,CRC功能必须关闭,Footer的长度为0。

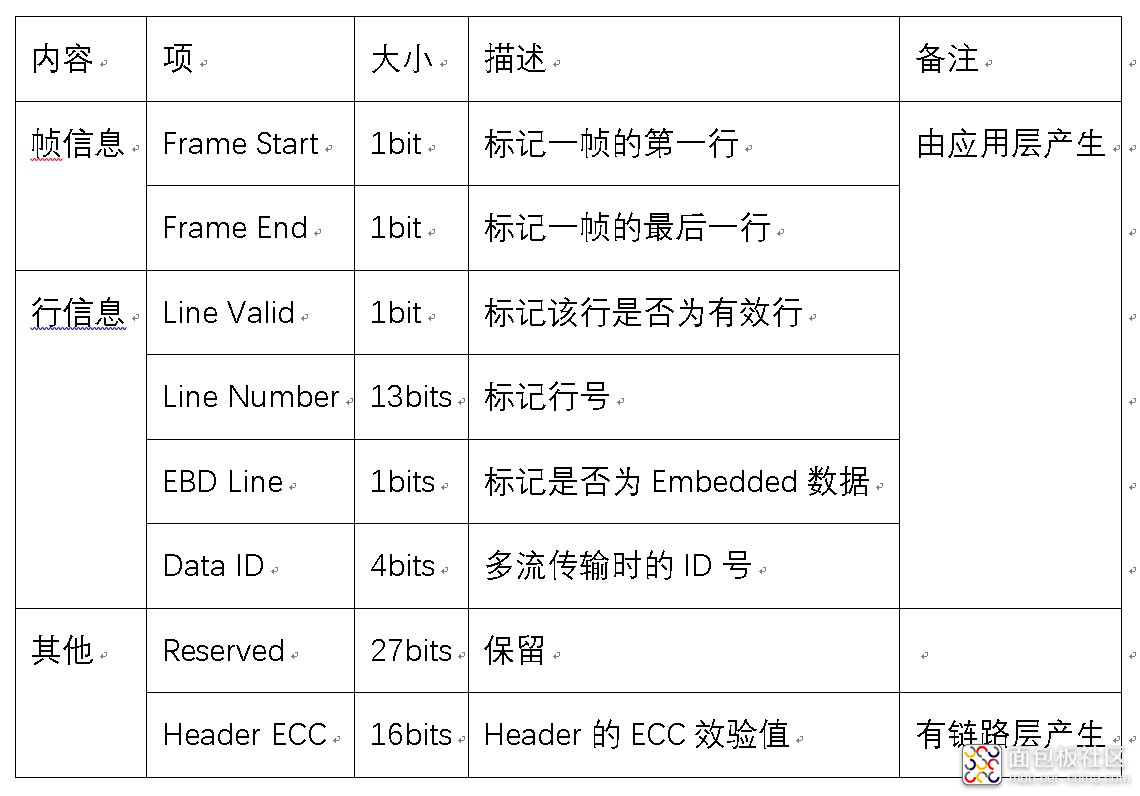

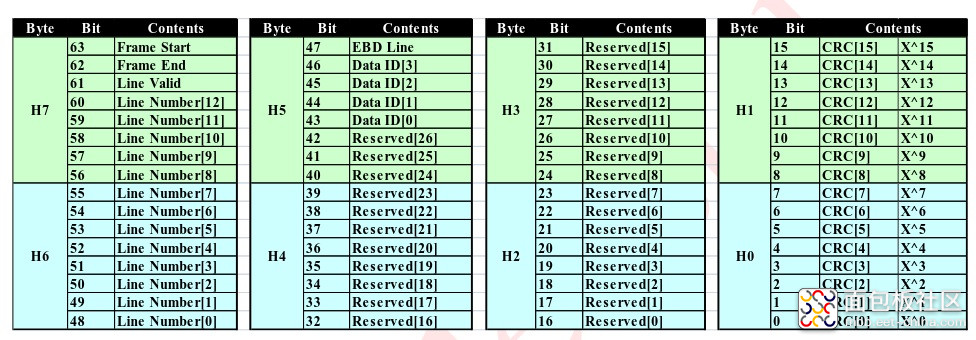

1.5.4 包头

包头(Packet Header)的长度固定为24字节,Packet Header的数据结构见下表1所示,共8字节,连续发三次,H7在Lane0的第一个字节,H6在Lane1的第一个字节,以此类推,H7~H0的顺序及定义如图6所示。

表1 Packet Header定义

图6 Packet Header 位定义

CRC为CRC16,多项式为X16+X15+X2+1,初始值为‘0’;

包尾(packet Footer)采用CRC32效验,多项式为X32+X31+X4+X3+X+1,初始值为‘0’。

1.5.5 物理层

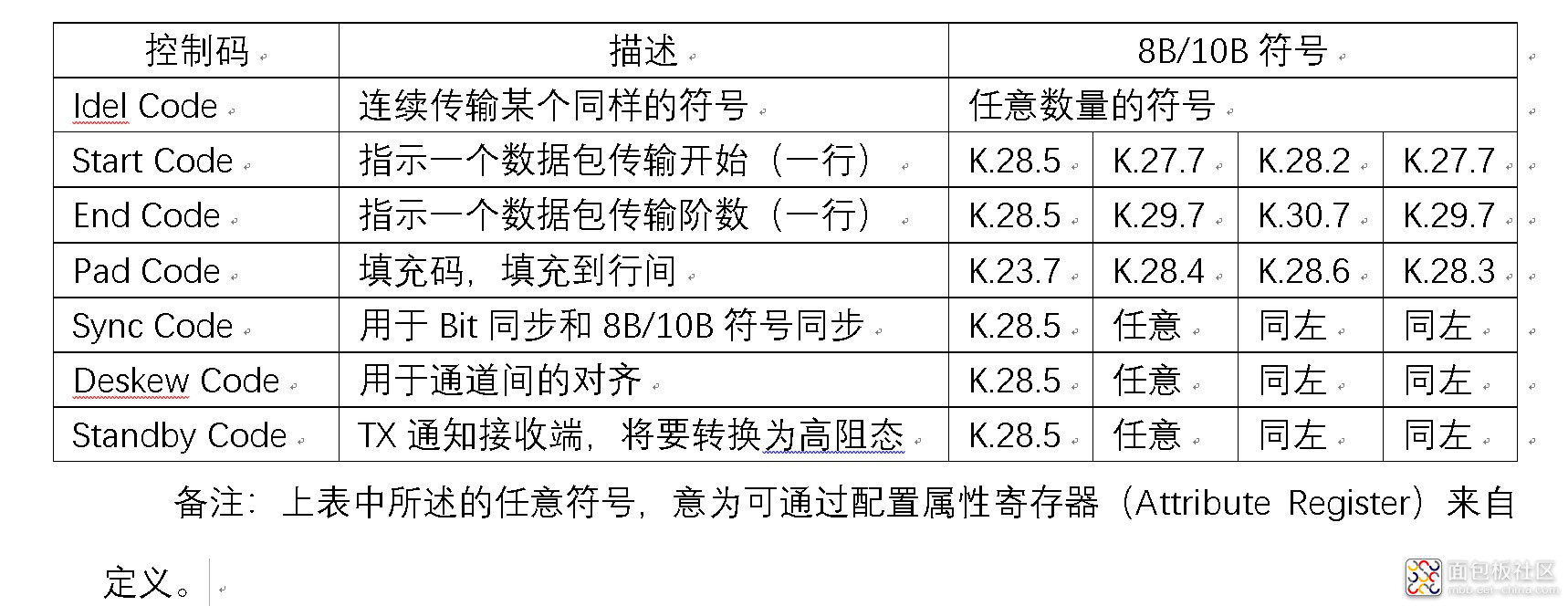

发送端物理层的作用是将发送一些列控制码和将数据载荷8B/10B编码后发送出去,接收端是发送端的逆过程。下表2是对控制码的定义。

表2 控制码定义

备注:上表中所述的任意符号,意为可通过配置属性寄存器(Attribute Register)来自定义。

Sync Code和Deskew Code的长度可通过Attribute Register进行定义,用做训练序列来做lane内bit同步和Lane间的对齐,来保证收端恢复数据和对齐通道。

SLVS-EC接口标准的主要内容大致就是这么多,其他的细节信息均可通过阅读手册来获取,由于熊猫君的水平有限,错误和疏漏之处在所难免,欢迎大家指正。大家可以通过QQ讨论群或微信公众号来一起讨论,学习,添加方式见下图,待熊猫君有空后,便码字分享第二部分“SLVS-EC接口FPGA实现”。文章开局的那张图便是实现SLVS-EC接口的FPGA板,CMOS图像传感器的型号为Sony的IMX421,配置为8通道SLVS-EC模式,满画幅输出(2/3英寸、2.86M像素),8bit/409.2fps。

作者: panda君, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-3403128.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/5

/5

panda君 2022-9-30 13:56