FPGA和DSP等功能复杂且需要多个电源的IC,以及需要多个系统电源的电子设备,可能会将电源的接通和关断顺序确定为一项产品规格。通用电源IC不遵守规格不仅不会正常启动,在某些情况下,甚至可能会使器件或设备受损。

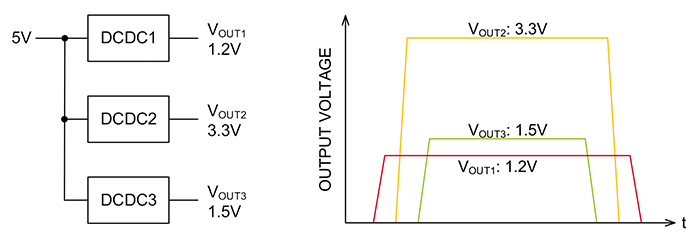

多个电源开/关时的顺序称为“电源时序”。下图是通用电源IC三个系统的电源相关的时序控制示意图。

控制电源时序的方法之一是使用电源时序控制专用IC。另外,电源IC中也有配备时序控制功能的IC和具有可支持时序控制的Power

Good输出等功能的IC,通过使用这些IC可以比较轻松地设计时序电路。在本系列文章中给出的电路示例,没有使用专用的电源时序控制IC以及具有时序控制功能的电源IC,而是通过仅具有输出开/关(使能)功能的通用电源IC和外部电路来实现电源时序控制。

作为示例,提供两种时序规格。后续将通过控制框图的结构、电路示例和工作示例来对每种规格进行解说。

首先,确认要实现的电源时序规格,并在设计实际电路之前通过控制模块来探讨其配置。本文会使用两个电源时序规格示例,先从第一个示例“电源时序 ①”开始。 电源时序规格① 规格①是控制3个系统的电源的时序。输入输出电压的规格和电源配置如下:

在本设计中,是由3个电源IC构成的。电源IC假定为开关稳压器(DC/DC转换器)或线性稳压器(LDO)。作为电源IC的功能,需要可以控制输出的ON和OFF的使能引脚。

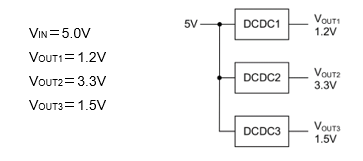

控制框图① 下面是实现了时序规格①的控制框图。

要实现时序规格①,除了3个电源IC之外,还需要4个Power Good功能、4个Discharge功能、以及电阻和二极管,从控制框图中可以看到它们。由于框图是为了显示功能和工作而绘制的,因此省略了实际电路中所需的各IC和电路的外置部件。下面介绍各功能和作用。 ・DCDC 1、DCDC 2和DCDC 3 是独立的电源IC,它们的输出由使能(EN)引脚控制。 ・Power Good 1和2用来在电源导通时监测DCDC的输出电压,当达到目标电压时,向接下来要启动的DCDC输出“High”(以下简称“H”)信号。 ・Power Good 3和4用来在关断电源时监测DCDC的输出电压,当达到目标电压时,向接下来要关断的DCDC输出“Low”(以下简称“L”)信号。 ・Discharge模块通过在关断电源时快速释放DCDC输出电容器中的充电电荷来降低输出电压,使电源时序正常工作。 在该框图中,DCDC模块的EN和VOUT之间、Power Good模块的IN和PGOOD之间、以及Discharge模块的IN和OUT之间被设计为正逻辑。也就是说,在“H”时,DCDC处于使能状态,Power Good处于达到目标电压状态,Discharge处于输出为ON的状态。此外,Power Good模块的PGOOD引脚(输出)和Discharge模块的OUT引脚采用集电极开路或漏极开路形式。

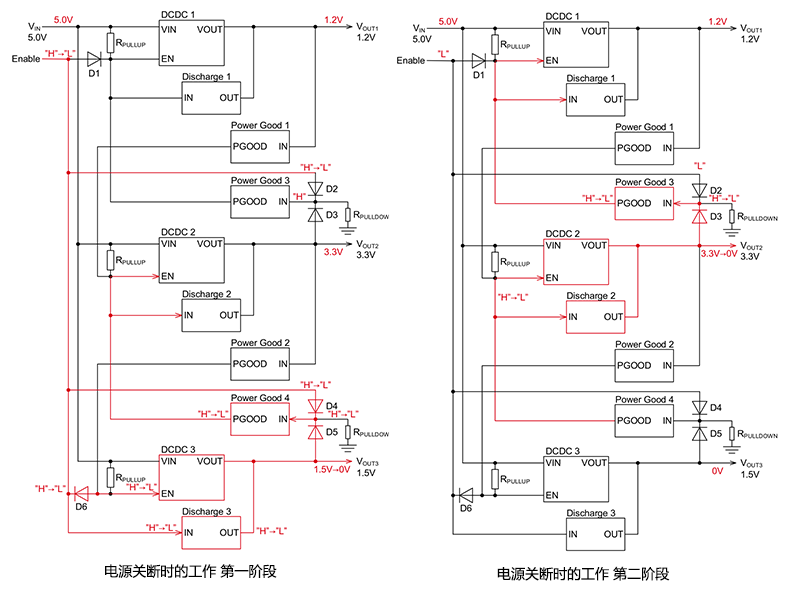

正如在之前的文章中介绍过的,规格①的时序是依次进行1.2V、3.3V、1.5V三个系统的输出。下面将按顺序对该时序工作进行说明。在介绍中,将施加1.2V的工作表述为“第一阶段”,将施加3.3V的工作表述为“第二阶段”,将施加1.5V的工作表述为“第三阶段”,将三个系统均导通的状态表述为“电源工作时”。在各阶段的图中,与说明相对应的部分用红色来表示。

在初始状态下,Enable引脚为“L”电平,三个DCDC输出均为零。

●第一阶段电源导通时的工作

●第二阶段电源导通时的工作

●第三阶段电源导通时的工作

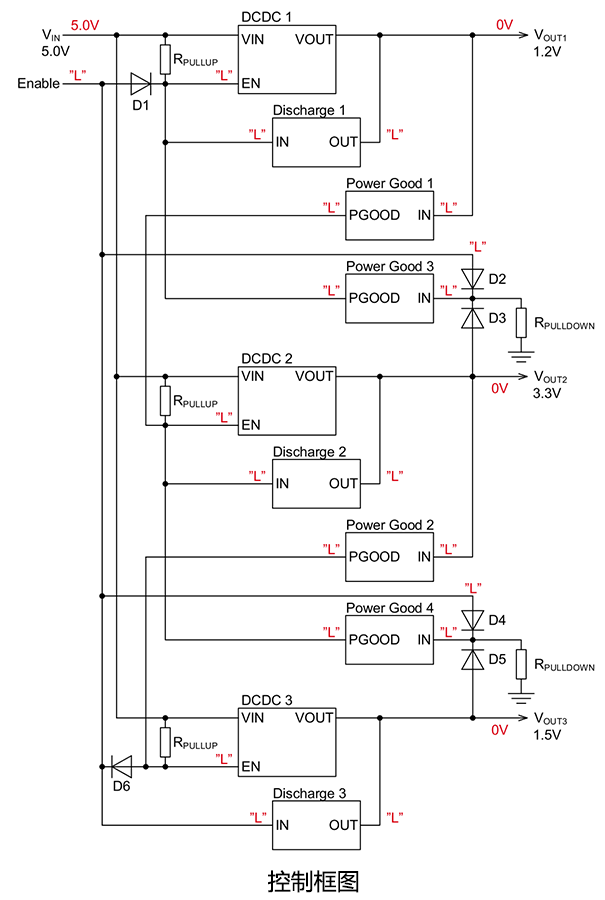

正如在之前的文章中介绍过的,规格①的时序是依次进行导通和关断的1.2V、3.3V、1.5V三个系统的输出。本文将继前一篇电源导通时的时序,来说明电源关断时的时序工作。电源按1.5V、3.3V、1.2V的顺序关断。在说明中,将关断1.5V的工作表述为“第一阶段”,将关断3.3V的工作表述为“第二阶段”,将关断1.2V的工作表述为“第三阶段”。在各阶段的图中,与说明相对应的部分用红色来表示。

第一阶段电源关断时的工作

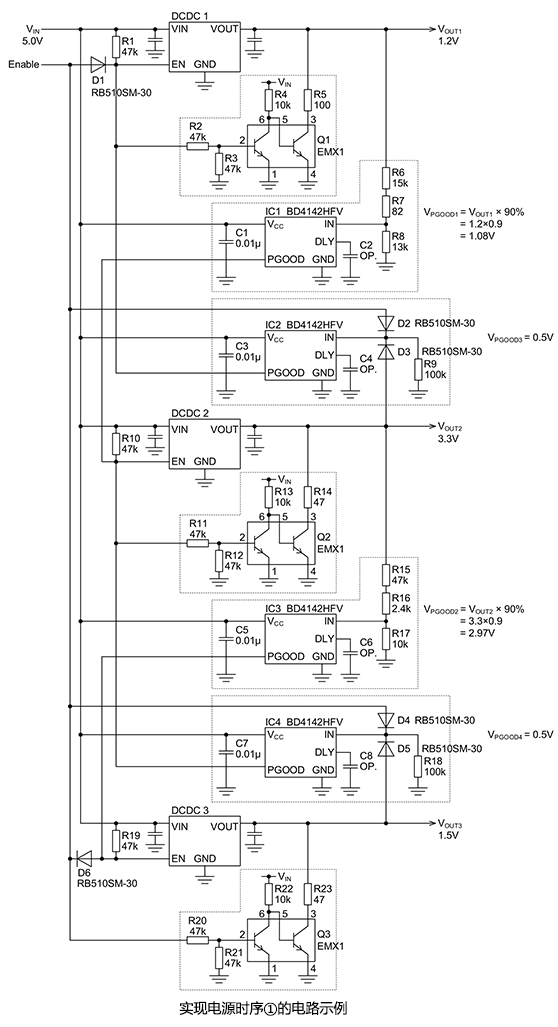

实现电源时序的电路示例如下所示。三个系统的DCDC 1~3假定为开关稳压器或线性稳压器(LDO)。每个DCDC都有使能(EN)引脚,可以控制输出的开和关。

实现电源时序①的电路示例

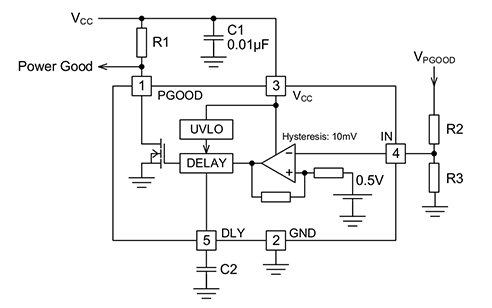

●Power Good模块共有4个Power Good模块,是使用电压监控ICBD4142HFV来实现Power Good功能的。IC1和IC3用于检测电源导通时DCDC输出电压是否上升到设定值,IC2和IC4用于检测电源关断时DCDC输出电压的下降情况。下图为包含BD4142HFV内部功能模块在内的Power Good电路。

由BD4142HFV组成的Power Good功能

该IC内置有迟滞比较器,基准电压为0.5V(见IC功能模块),可以使用外置分压电阻设置想要检测的电压。用来检测DCDC输出电压上升情况的IC1和IC3,需要根据DC/DC的输出电压进行该设置。检测电压VPGOOD可通过公式1-1来计算。

![]()

时序电路示例的VOUT1为1.2V,IC1的PGOOD设置为当达到输出电压的90%时输出一个标志。如果检测电压设置得过高(如95%),当输出电压因负载波动而瞬间下降时,PGOOD输出将变为“L”,会造成后段DCDC瞬断的问题。因此需要在了解了DCDC的负载波动和压降(负载响应)特性后,再确定检测电压。

在90%时的检测电压为1.2V×0.9=1.08V。电阻值可以根据公式1-1来计算。计算出来的电阻值已在电路示例的IC1处标出,公式1-1中的R2对应于电路示例中的R6:15kΩ+R7:82Ω,R3对应于R8:13kΩ。将这些值代入后公式如下,结果表明该常数是可以获得所需的1.08V的常数。

![]()

从公式中可以看出,需要针对VPGOOD确定电阻值,以使R2和R3施加到IN引脚的分压电压变为内部基准电压0.5V。电压是由电阻比决定的,但由于该分压电阻也是DCDC的负载,因此采用10kΩ级的电阻值比较合适。但是,R2和R3的总和要在300kΩ以内。如欲了解更详细的信息,请参阅IC的技术规格书。

这样,基本的常数就确定了,但作为设计,还需要确认设置值(检测电压)的容差。BD4142HFV的检测电压容差为±1.8%。因此,PGOOD的范围是从88.4%(90%-1.8%=90×0.982)到91.6%(90%+1.8%=90×1.018)。

另外,由于有10mV的迟滞,因此检测解除电压为90%×(0.5V-10mV)÷0.5V=88.2%,范围为88.2%×0.982=86.6%到88.2%×1.018=89.8%。

此外,BD4142HFV在PGOOD标志输出中也可以有延迟时间tDELAY。在这种情况下,要将电容器C2连接到DLY引脚。延迟时间和电容器C2的值可以通过公式1-2来计算。

![]()

当DCDC的输出电压降至约0.5V以下时,在电源关断时工作的PGOOD的IC2和IC4将会停止检测(PGOOD输出将从“H”变为“L”)。这是直接使用BD4142HFV已设置好的检测电压。

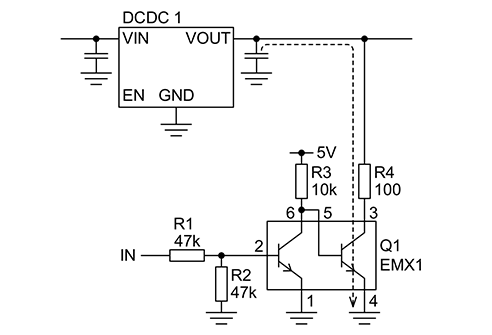

●放电电路在该电路中,分立结构的放电电路连接到每个DCDC。如下图所示,该电路由NPN晶体管和电阻组成。第一段的晶体管是简单的逆变器电路,第二段是集电极开路开关。第二段导通时,在DCDC关断时主要是释放输出电容器的残余电荷,使VOUT迅速下降。输出电压的下降时间根据与第二段晶体管的集电极串联的电阻(下图中的R4)值来调整。

放电电路

时序电路示例中各处的二极管用于控制逻辑工作。由于二极管的正向电压VF会影响“L”电平的信号电压,因此需要使用VF较低的肖特基势垒二极管来确保“L”电平的电压值。

对使用通用电源IC实现电源时序控制时实现电源时序①的整个电路、以及作为DCDC之外的外围电路的Power Good模块、放电电路、二极管的介绍就到这里。

下面的电路是实现上一篇中的的电源时序①的电路示例。在这里再次给出是为了便于确认电路工作。

接下来是实际的工作波形。

当VOUT3低于Power Good模块IC4的阈值0.5V时,IC4的PGOOD输出会禁用DCDC 2并同样导通放电电路以降低VOUT2。

当VOUT2低于Power Good模块IC2的阈值0.5V时,如前一阶段一样,IC2的PGOOD输出会禁用DCDC 1并导通放电电路以降低VOUT2。

这样就完成了三个关断时序并关闭所有输出。

来源:techclass.rohm

/5

/5

文章评论(0条评论)

登录后参与讨论