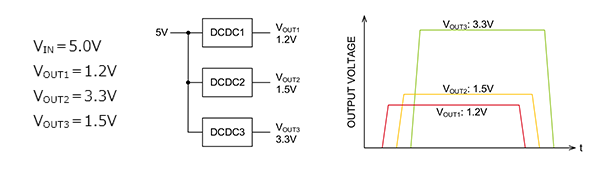

电源时序规格②与①一样有3个系统的电源时序,但时序不同。输入输出电压的规格、电源配置及时序如下:

规格②的设计由3个电源IC组成。电源IC假定为开关稳压器(DC/DC转换器)或线性稳压器(LDO)。作为电源IC的功能,需要可以控制输出的ON和OFF的使能引脚。

电源导通按照VOUT1、VOUT2、VOUT3的顺序,当VOUT1导通并达到设置电压时,VOUT2导通,同样,达到设置电压时VOUT3导通。关断时序与输入时序一样,按照VOUT1、VOUT2、VOUT3的顺序,当VOUT1关断完成后,VOUT2关断,然后VOUT3关断。

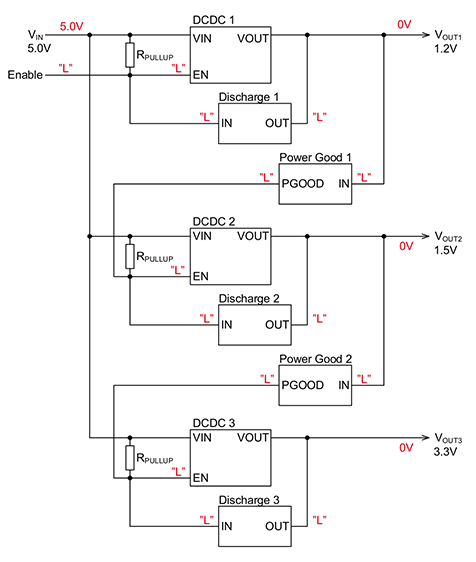

控制框图②下面是实现了时序规格②的控制框图。

要实现时序规格②,除了3个电源IC之外,还需要2个Power Good功能、3个Discharge功能,另外还需要上拉电阻。框图是为了显示功能和工作而绘制的,在实际电路中,还需要其他外置元器件。下面介绍各功能和作用。

・DCDC 1、DCDC 2和DCDC 3 是独立的电源IC,它们的输出由使能(EN)引脚控制。

・Power Good 1和2用来在电源导通时监测DCDC的输出电压,当达到目标电压时,向接下来要启动的DCDC输出“High”(以下简称“H”)信号。

・在关断电源时,Power Good 1和2均用来监测DCDC的输出电压,当低于目标电压时,向接下来要关断的DCDC输出“Low”(以下简称“L”)信号。

・Discharge模块通过在关断电源时快速释放DCDC输出电容器中的充电电荷来降低输出电压,使电源时序正常工作。

在该框图中,DCDC模块的EN和VOUT之间、Power Good模块的IN和PGOOD之间、以及Discharge模块的IN和OUT之间被设计为正逻辑。也就是说,在“H”时,DCDC处于使能状态,Power Good处于达到目标电压状态,Discharge处于输出为ON的状态。此外,Power Good模块的PGOOD引脚(输出)和Discharge模块的OUT引脚采用集电极开路或漏极开路形式。

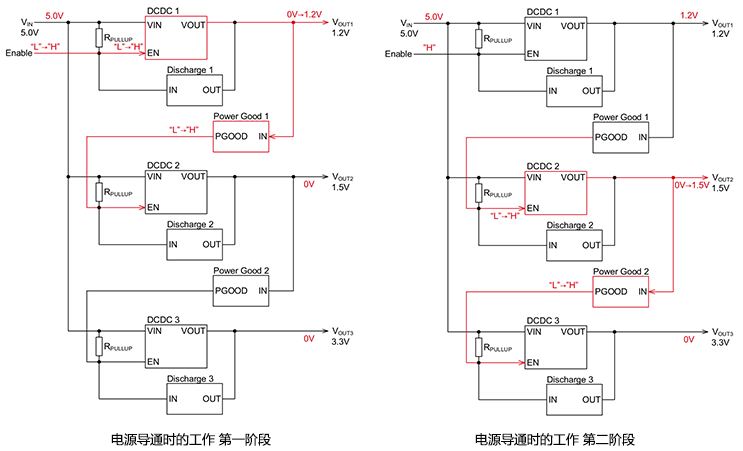

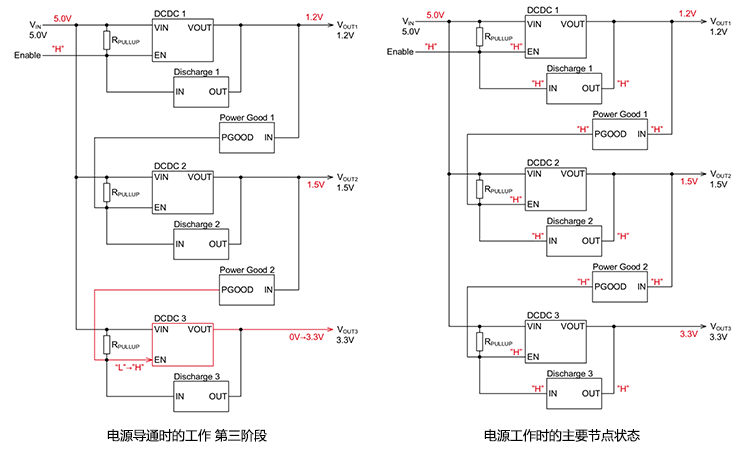

如上一篇文章所述,规格②的时序是1.2V、1.5V、3.3V这三个系统的输出按照该顺序依次导通并按相同顺序依次关断。下面分步讲解电源导通时的时序工作(关断时的时序工作将在下一篇文章中进行讲解)。在下面的讲解中,将施加1.2V的工作表述为“第一阶段”,将施加1.5V的工作表述为“第二阶段”,将施加3.3V的工作表述为“第三阶段”,将三个系统均导通的状态表述为“电源工作时”。在图中,与各阶段的说明相对应的部分用红色来表示。

在初始状态下,Enable引脚为“L”电平,三个DCDC输出均为零。

第一阶段电源导通时的工作

以上是使用通用电源IC实现电源时序控制时电源时序规格②的电源导通时的时序工作。在下一篇文章中,将会介绍使用通用电源IC实现电源时序控制时关断时的时序工作。

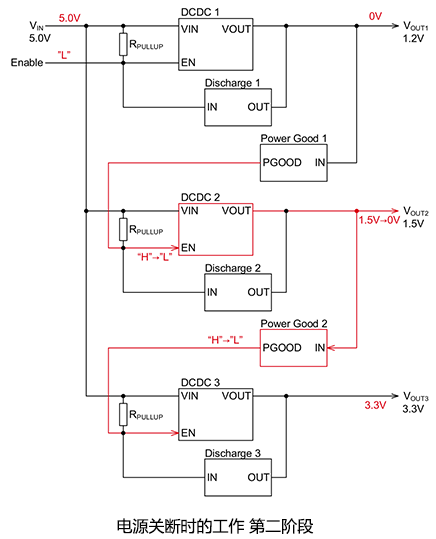

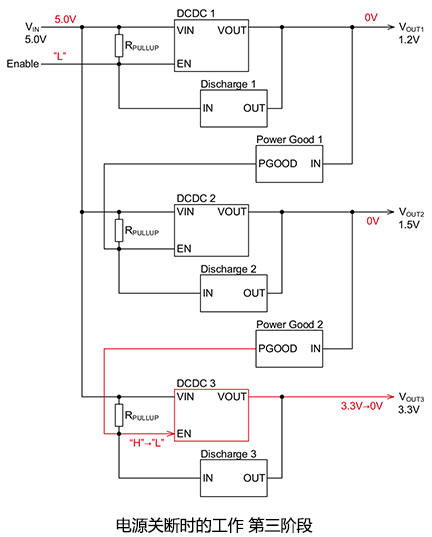

如此前的文章所述,规格②的时序是1.2V、1.5V、3.3V这三个系统的输出按照该顺序依次导通并按相同顺序依次关断。在说明中,将关断1.2V的工作表述为“第一阶段”,将关断1.5V的工作表述为“第二阶段”,将关断3.3V的工作表述为“第三阶段”。在各阶段的图中,与说明相对应的部分用红色来表示。

●第一阶段电源关断时的工作

●第二阶段电源关断时的工作

●第三阶段电源关断时的工作

以上是使用通用电源IC实现电源时序控制时电源时序规格②的电源关断时的时序工作。下一篇将会探讨使用通用电源IC实现电源时序控制时实际的电路和常数等的设置示例。

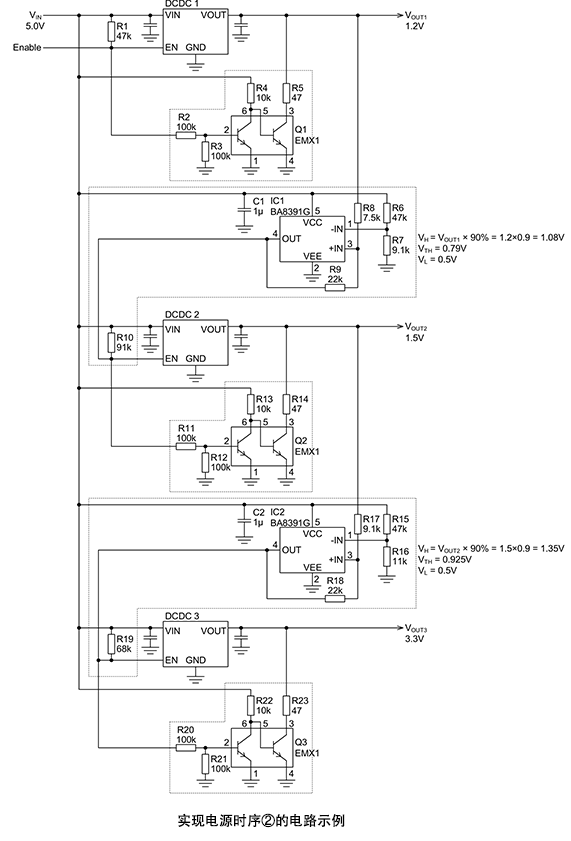

实现电源时序②的电路示例如下所示。三个系统的DCDC 1~3假定为开关稳压器或线性稳压器(LDO)。每个DCDC都有使能(EN)引脚,可以控制输出的开和关。

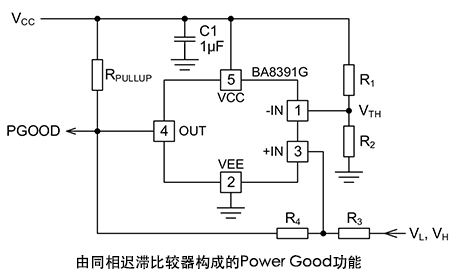

有两个Power Good模块。在规格①中,Power Good功能是使用电压监控IC BD4142HFV实现的,但在规格②中,则由下图所示的同相迟滞比较器实现,IC则使用比较器IC BA8391G。

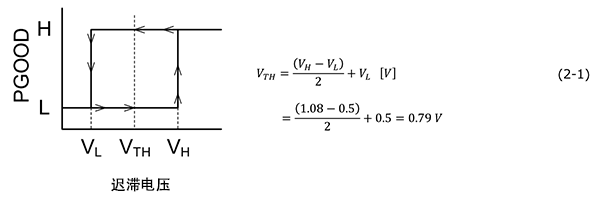

启动时的检测电压VH和关断时的检测电压VL之间设有较大的迟滞电压。这使得通过1个器件来检测启动时和关断时的电压并输出控制信号成为可能。

下面以上述电路示例中的VOUT1为例,计算每个常数。VOUT1为1.2V,IC1的PGOOD设置为在达到输出电压的90%时输出一个标志。启动时的检测电压VH为1.2V×0.9,即1.08V。关断时的检测电压VL设置为0.5V。这是即使在每个电源之间施加反向电压,寄生元件大概也不会导通的电压。

比较器的阈值电压VTH设置在VH和VL之间的中点,如下所示。该值可以通过公式2-1来计算。

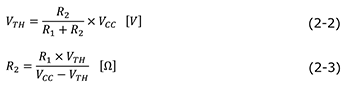

另外,VTH也可以用公式2-2来表示,当为了求得R2而将公式2-2变形后,就成为公式2-3。

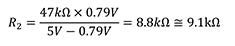

设R1为47kΩ,VCC由VIN提供所以是5V,R2根据以下公式变为8.8kΩ。从E24系列电阻阻值速查表中选择标称电阻值9.1kΩ。

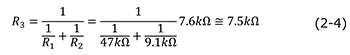

R3选择与反相输入引脚(-IN)的阻抗相同的产品,以抵消输入偏置电流。根据公式2-4得出的值为7.6kΩ,从E24系列电阻阻值速查表中选择标称电阻值7.5kΩ。

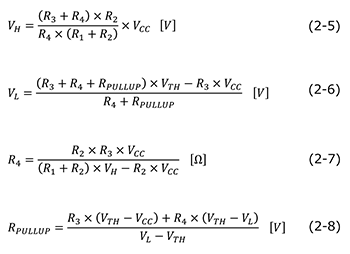

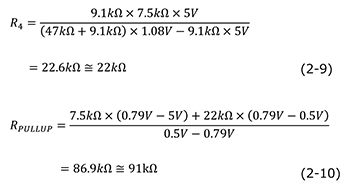

计算同相迟滞比较器的VH和VL的常用计算公式为2-5和2-6。当这些公式被转换为计算R4和RPULLUP的公式时,就会变成公式2-7和2-8。

将前面求得的常数代入公式2-7和公式2-8,再求出剩余值。

对VOUT2的Power Good模块也按照相同的步骤进行常数计算。请参考本文开头给出的整体电路示例。

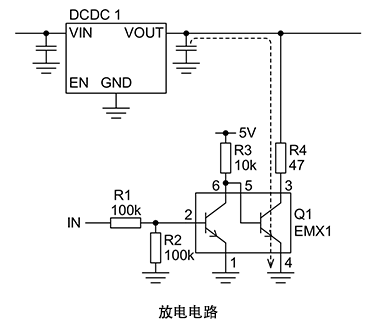

●放电电路在该电路中,分立结构的放电电路连接到每个DCDC。如下图所示,该电路由NPN晶体管和电阻组成。第一段的晶体管是简单的逆变器电路,第二段是集电极开路开关。第二段导通时,在DCDC关断时主要是释放输出电容器的残余电荷,使VOUT迅速下降。输出电压的下降时间根据与第二段晶体管的集电极串联的电阻(下图中的R4)值来调整。这部分与规格①相同。

下面的电路是实现上一篇中的的电源时序②的电路示例。在这里再次给出是为了便于确认电路工作。

实现电源时序②的工作波形如下所示。

当VOUT1低于Power Good模块IC1的阈值VL(即0.5V)时,IC1的OUT输出会禁用DCDC 2,同时导通放电电路,以降低VOUT2。

当VOUT2低于Power Good模块IC2的阈值VL(即0.5V)时,如前一阶段一样,IC2的OUT输出会禁用DCDC 3并导通放电电路以降低VOUT3。

这样就完成了三个关断时序并关闭所有输出。

/5

/5

文章评论(0条评论)

登录后参与讨论