随着研究人员开始开发和测试下一代晶体管,铁电FET和存储器开始显现出美好前景。

晶体管效率的一个衡量标准是亚阈值摆幅,即将漏极电流增加一个数量级所需的栅极电压的变化。以每十倍毫伏为单位测量,在传统MOSFET中,通过玻尔兹曼电子能量分布将其限制为kT / q。这在室温下约为60 mV / decade。

随着器件尺寸的微缩,这一限制变得更加麻烦。如果电源电压恒定,则需要越来越高的电荷密度来产生相同的电流量。

器件设计人员有两种方法可以降低亚阈值摆幅(SS)。它们可以使用具有不同物理特性的不同开关机制,例如隧道FET,或者他们可以找到一种方法来增加栅极电容,而不增加栅极电压。后一种选择促使人们对铁电晶体管(FeFET)产生极大的兴趣,铁电晶体管将铁电电容器与传统的介电栅极电容器串联。

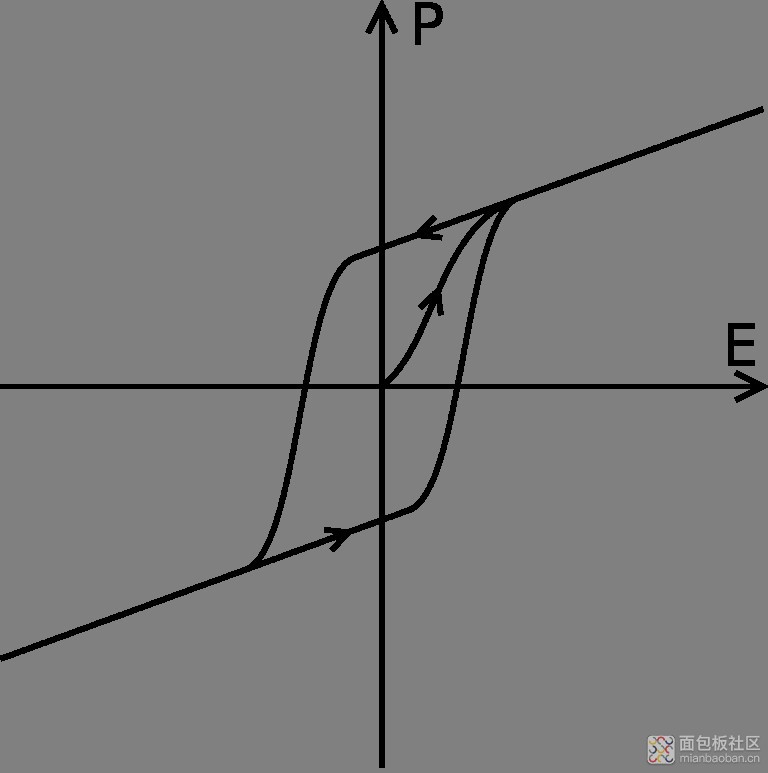

铁电材料作为潜在的非易失性存储元件首次引起了业界的关注。铁电材料具有内置的电子偶极矩。(它们因类似于铁磁材料而得名,实际上铁电体通常不含铁。)施加足够强的电场会使材料的极化反转,并且即使在去除电场之后极化仍然存在。极化的衰减率 - 材料的滞后 - 产生“存储窗口”,其允许铁电电容器存储先前的充电状态。FeRAM设备正是基于这一行为方式。

图1:作为电场函数的铁电极化。资料来源: 维基媒体

负电容解释

在正极和负极化状态下,铁电电容表现为传统电容,具有正电容εA/ d。(A是板的面积,d是它们之间的间隔,ε是电介质的介电常数。)

正如Imec首席科学家Anne Verhulst在最近的IEEE电子设备会议(IEDM)上所做的工作中所解释的那样,切换极化会导致铁电(MFM)电容器的电荷瞬间下降。如果MFM电容与晶体管的栅极(MIS)电容串联,则该瞬态会使栅极电荷增加。所谓的“负电容”效应可以在晶体管的电压 - 电流曲线的至少一部分上产生低于60mV /十倍的亚阈值摆幅。2011 年HfO 2中铁电行为的发现使FeFET成为CMOS兼容的潜在解决方案,解决了业界最具挑战性的扩展问题之一。

也许,在FeRAM器件中如此有用的滞后有助于FeFET中的开关延迟。目前尚不清楚无滞后器件是否仍会表现出负电容效应,特别是在前沿电路所需的高开关速度下。关于负电容效应是FeFET结构的基本特征,电荷俘获的不可靠伪像,或两者的程度,一直存在争论。在IEDM,一些协议点开始出现。

优化FeFET

共识FeFET(或NCFET)结构似乎是具有TaN电极的铪 - 锆氧化物(HZO)电容器,放置在HfO 2栅极氧化物的顶部。(在一些实验研究中使用SiO 2氧化物。)东京大学的Chengji Jin及其同事发现,增加锆含量会增加电容并最终导致反铁电行为,磁滞回线顺时针而不是逆时针移动。大多数提出的装置具有大致相等量的铪和锆。

Shinji Migita(AIST,Ibaraki,日本)指出,MFM电容器中的电荷可以比MIS电容器多得多。他的组装置使用10nm厚的Hf 0.5 Zr 0.5 O 2,最大电荷密度为30μC/ cm 2,结合3.8nm厚的SiO 2,其最大电荷密度为2.7μC/ cm 2。向栅极电容注入太多电荷最多是无益的,最坏的情况是导致电介质击穿。

因此,通过匹配两个器件的电容来实现最佳结果。虽然大多数研究通过调整顶部(MFM)电容器的面积来做到这一点,但优化的生产工艺可以将两个电容器的厚度和面积视为可调参数。几个小组在区域匹配的FeFET器件中展示了无滞后的陡峭SS性能。

下一个重要的挑战是铁电极化的动力学。切换铁电电容器的极化需要有限的时间。

铁电层中的各个晶粒是二元的 - 它们在任何特定时刻都是正极化或负极化。加州大学伯克利分校的Yen-Kai Lin及其同事进行了模拟,其中铁电体是多晶的,具有一定的晶粒尺寸和开关场分布。减小开关场并增加脉冲速率 - 这两者在商业设备中都是期望的 - 可导致不均匀的铁电行为和不一致的电流。

界面和结晶质量差会引入电荷陷阱,从而在一定程度上抵消铁电行为。

超越路线图:负电容和新兴器件

虽然负电容晶体管的大部分兴趣都是针对更近点的平面MOSFET和finFET结构,但一些研究人员也将这一概念应用于新兴器件。在Imec,单晶PZT电容与InGaAs TFET的栅极串联,产生的SS值低至40 mV / decade。国立台湾师范大学的研究人员在具有HZO门的高尺度栅极全纳米片状FET中实现了更低的SS,平均22 mV / decade。最后,香港理工大学的一个小组使用HZO / Al 2 O 3叠层作为二维WSe 2晶体管的栅极,实现了最小18.2 mV / decade SS。

这些结果都表明,铁电电容器可以为任何提出的后MOSFET结构提供通用性能提升。

译自Semiconductor Engineering, BY: KATHERINE DERBYSHIRE

/5

/5

Rain社区管理 2019-4-24 09:32

1451262183_584877486 2019-1-9 10:34