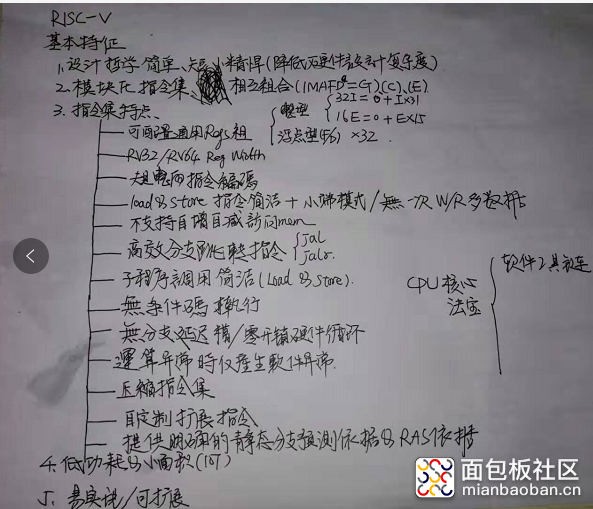

挤出时间来大致粗读了本书的部分内容,受益匪浅。整体来讲,本书写的通俗易懂,有足够详细的实例,开放的源代码,让初学者爱不释手。由于时间仓促,本人阅读时大致做了一些笔记,收获不小。粗略知道RISC-V指令的基本特点与优点,如图1.1所示;

图1.1:RISC-V 指令集基本特点

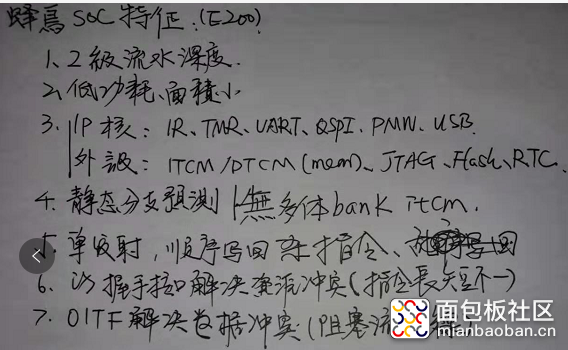

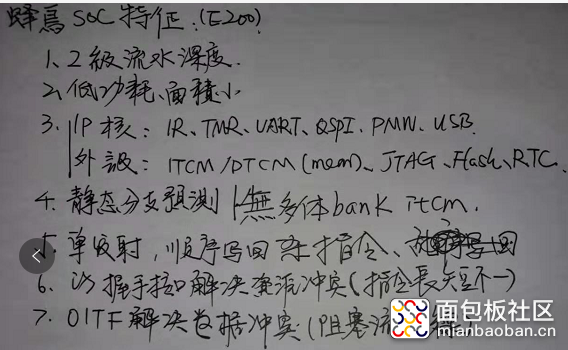

同时整本书内容安排逻辑性强,环环相扣;详细介绍了低功耗了嵌入式蜂鸟E200系列SOC,实现原理与详细设计过程。整个SOC也呈现出如下特点图1.2:

图1.2:蜂鸟E200 SOC系列 core 特点

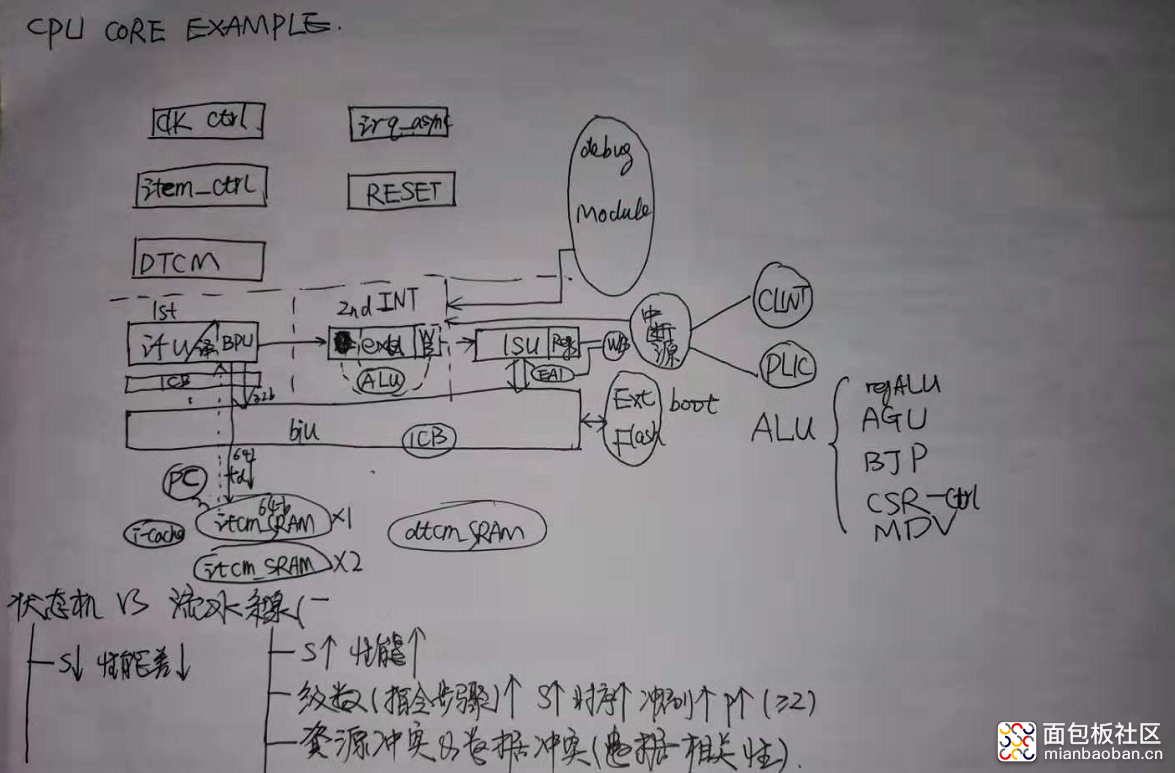

详细介绍了Verilog HDL 设计CPU的各个模块,使本人对N级流水线各个步骤、cpu core、硬件设计逻辑等有了新的认识。图1.3展现了一个SOC example(以蜂鸟E200为蓝本),

图1.3:soc 通用架构(以蜂鸟E200 example)

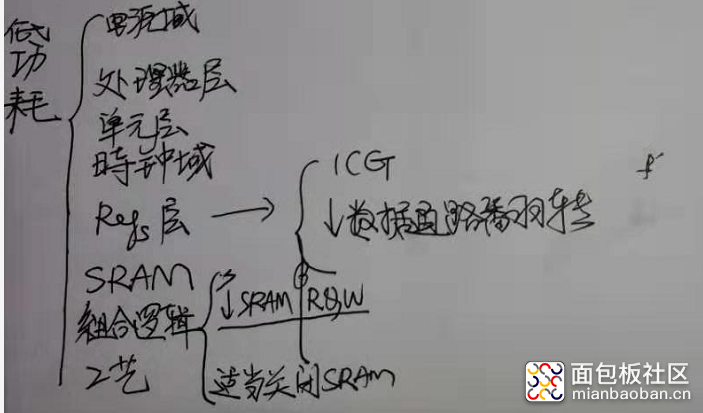

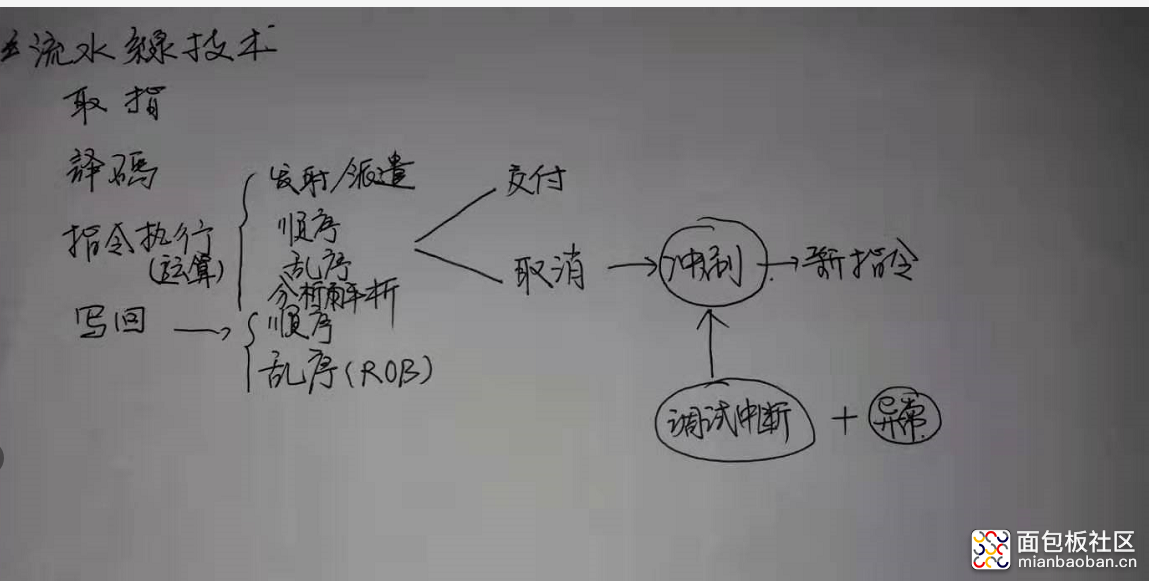

通过大量的篇幅来介绍蜂鸟E200 内部流水线的各个部件工作原理和实现过程。蜂鸟E200内部的2级流水线关键信息如图1.4所示:

图1.4:蜂鸟E200 2级流水线example

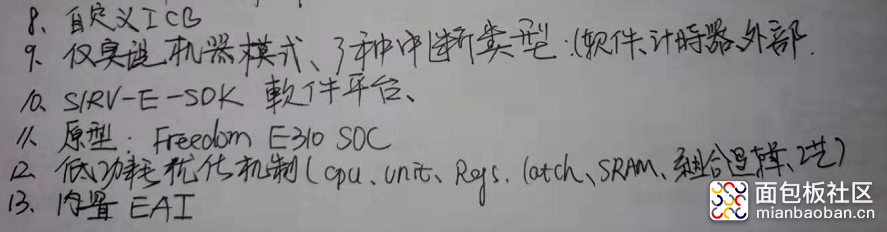

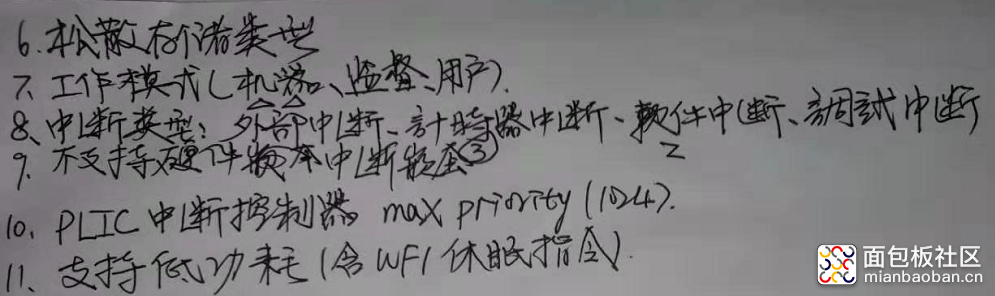

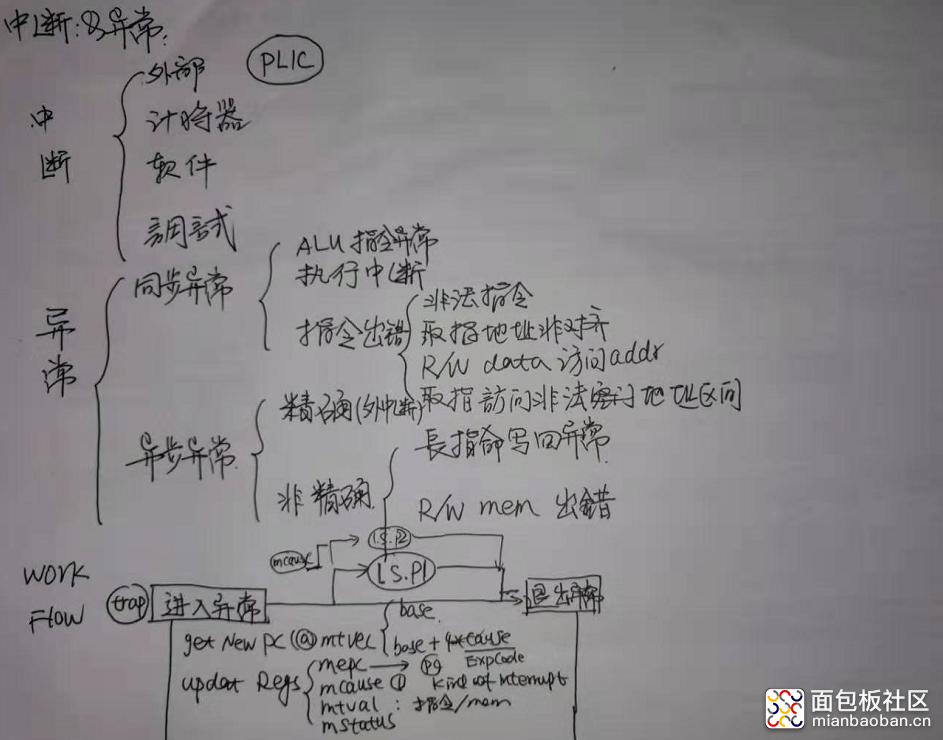

紧接着介绍了中断和异常,同时介绍了RISC-V架构异常处理机制、中断类型、屏蔽、等待、嵌套、优先级与仲裁机制以及蜂鸟E200异常处理的硬件实现原理。中断与异常的概述如图1.5:

图1.5:中断与异常的概述

由于RISC-V指令架构具有一定的拓展性,蜂鸟E200利用此特点设计了EAI(协处理接口),同时给出了EAI的工作时序,信号定义,此处不作赘述。

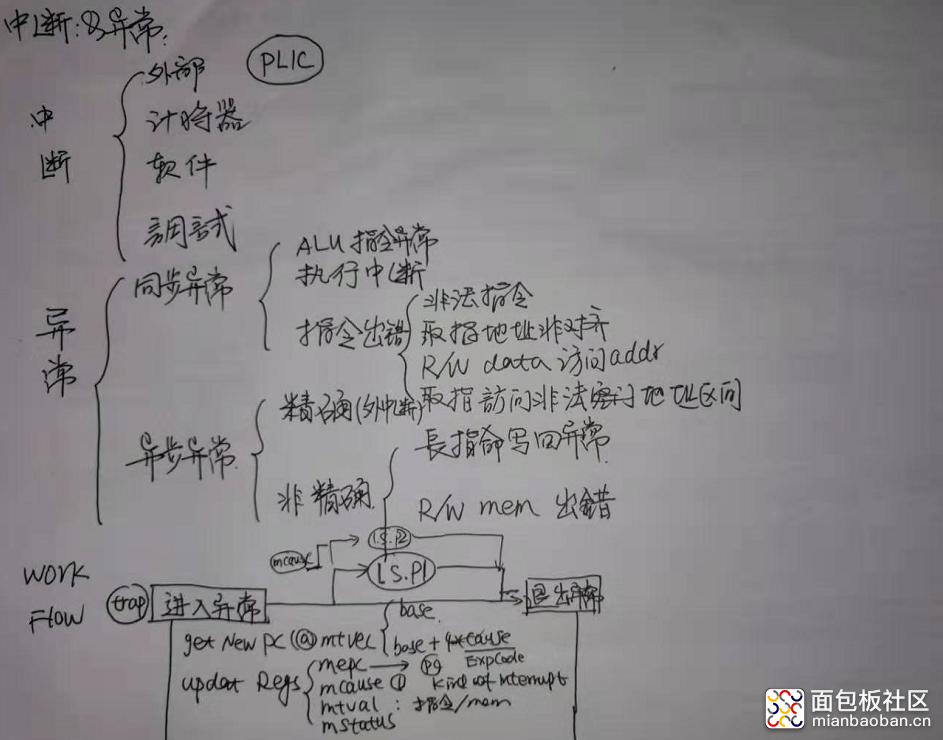

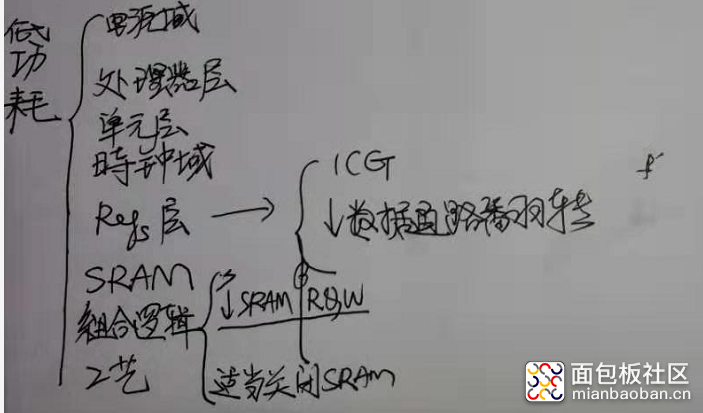

并给出了几种SOC低功耗优化的几个思路,以及蜂鸟E200低功耗优化的具体实现方法,如图1.6所示:

图1.6:SOC 低功耗优化策略

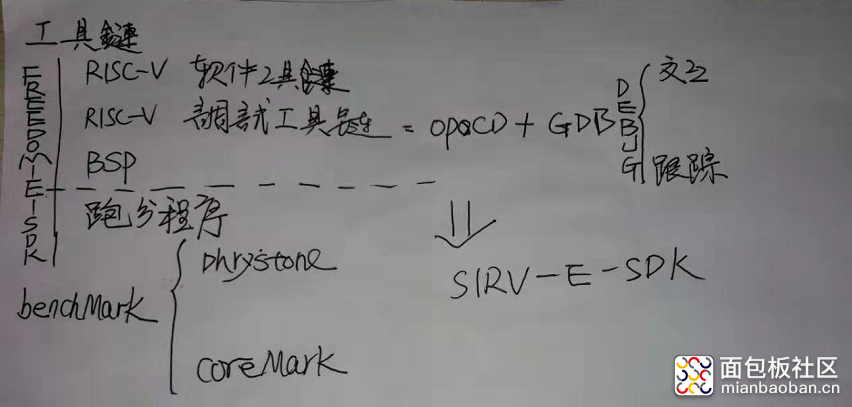

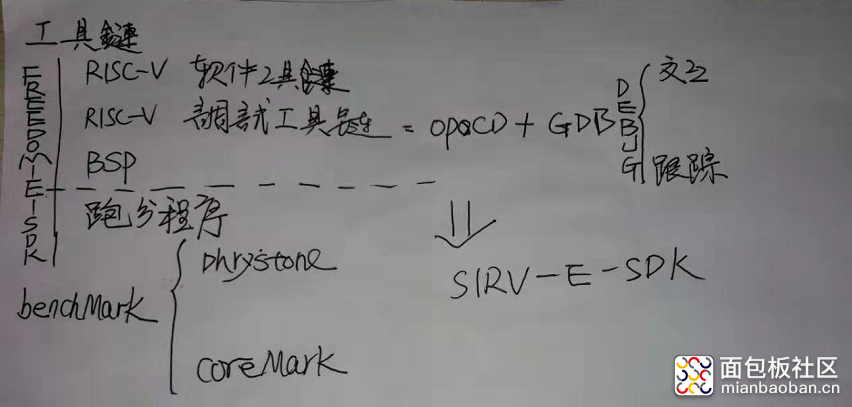

最后一部分,本书简要给出了蜂鸟E200的基于FPGA SOC的原型运行与调试。简要介绍了相关工具链Freedom-E-SDK,以及SIRV-E-SDK(Freedom-E-SDK的优化版)。Freedom-E-SDK的简要组成如1.7所示:

图1.7:Freedom-E-SDK简要组成

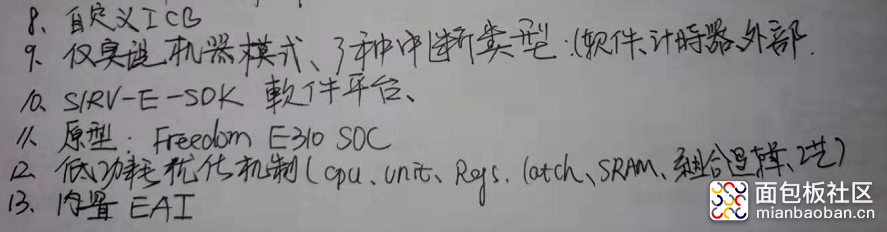

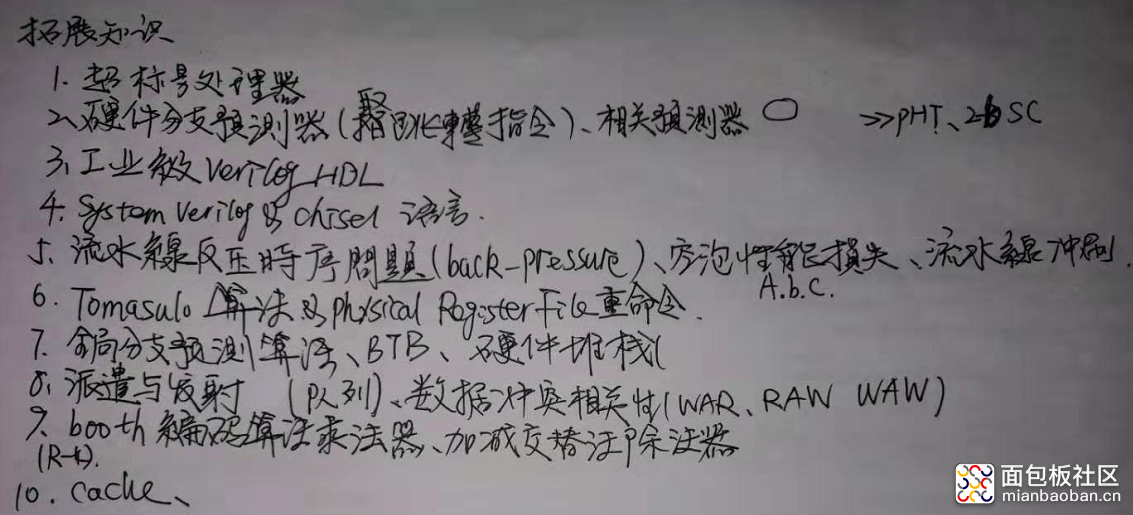

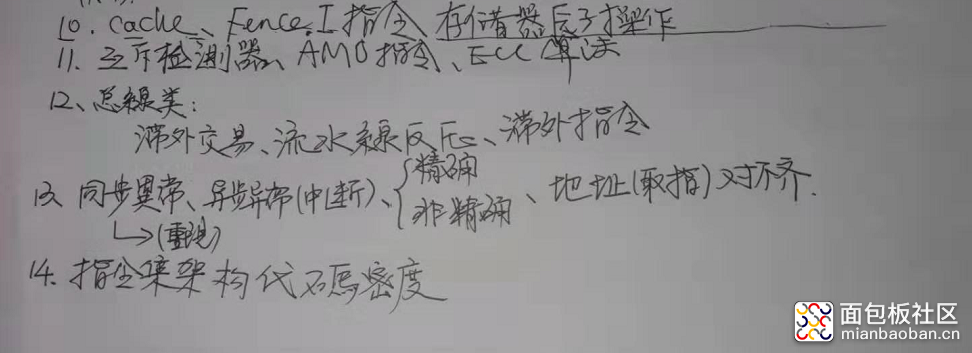

在阅读过程中也遇到了自己未知的和不了解的,还需要后续查阅资料搞明白,本人认为比较重要的学问(对其他学习者提供参考),如图1.8所示:

图1.8:未知知识记录

【读后感】

由于时间仓促,只能走马观花,大概一览。其中具体实现原理和细节,还需要花大量时间更深一步的如切如磋,如琢如磨。虽然本人现在从事RF芯片测试工作,与设计无关。但是从对SOC内部架构有了更深印象和更独特的理解,对设计方法,设计思想有更深地了解。感谢提供此资源和源代码的所有工作人员。在阅读的过程中,让我体会到:

1.学无止境,学海无边同时精一专一;

2.基础知识的重要性【通过对RISC-V浅显学习,之前在学习微机原理时不明白的地方,顿时茅塞顿开】;

3.学科交叉

4.以此为起点,研究出国产的自主知识产权的指令集、工具链(编译器、调试器、仿真器)等。

/5

/5

curton 2019-10-15 19:51

shwnyoo 2019-10-14 21:50