Si IGBT/MOSFET与SiC MOSFET,尽管衬底材料不一样,但是形成栅极氧化层的材料却是一样的——都是SiO2。SiC-SiO2界面缺陷大于Si-SiO2界面,界面缺陷会降低反型层沟道迁移率,进而提高沟道电阻。对于SiC MOSFET,尽管人们花了很多精力来提高沟道迁移率,但其迁移率仍然远远低于硅的IGBT/MOSFET。

(更详细的解释请参考:SiC MOSFET真的有必要使用沟槽栅吗?)

因此,商用SiC MOSFET会设计成具有相对较短的反型层沟道,以尽量减少其沟道电阻。对于1200V的SiC MOSFET来说,沟道电阻对整个RDS,on的贡献最大,这与高压Si MOSFET完全不同。此外,对于沟槽MOSFET,由于SiC漂移区厚度较低,基极掺杂较高,因此沟道区附近的电场强度(特别是在开关期间)比Si MOSFET高。为了保护栅极氧化物,必须有一个屏蔽结构,这在所有现代SiC MOSFET概念中都可以找到。与硅器件相比,上述效应导致了更明显的漏极势垒降低效应(DIBL-或短沟道效应)。DIBL效应的原理大家可以在百度搜到,这里就不再赘述了。DIBL效应造成的明显的现象是——随着漏极-源极电压VDS的增加,栅-源极阈值电压VGS(th)会随之降低,见图1。

Fig.1:不同制造商1200V SiC MOSFET的VGS(th)曲线,Infineon-沟槽,M1-沟槽,M2-平面

DIBL效应和栅极电荷

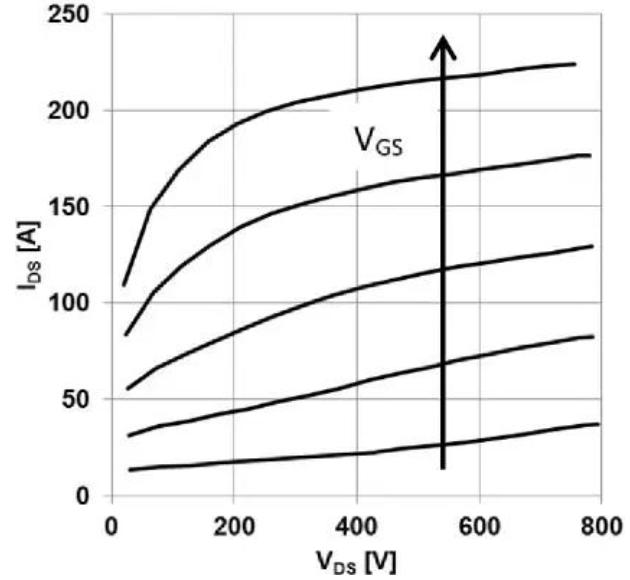

由于上述的DIBL效应,与IGBT相比,SiC MOSFET的输出特性看起来有所不同。在相同VGS条件下,器件的饱和电流随VDS上升而上升。见图2。

图2:45mΩ、1200V SiC沟槽MOSFET在25°C时不同VGS下的输出特性曲线。该特性是在短路状态下,通过非常短的脉冲测量的,并在考虑到测量期间温度上升的情况。

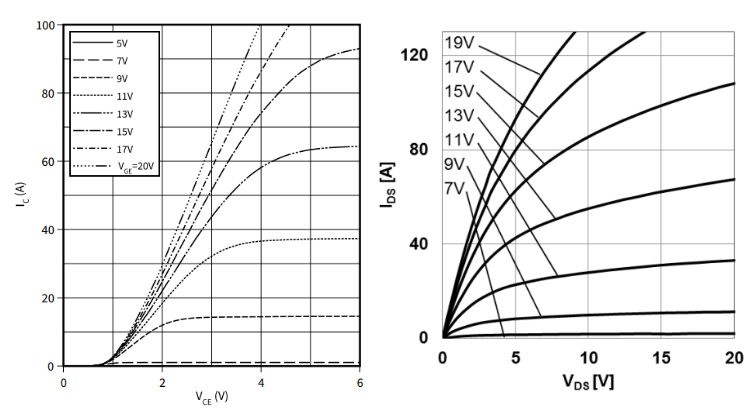

硅IGBT通常使用更长的反型沟道,沟道电阻对静态损耗来说是次要的。阻断状态下的电场较小,因此,DIBL效应较低,饱和电流不会随DS电压上升而变化太大。下图(左)是IGBT的输出特性曲线,可以看到,线性区和饱和区之间的分界点很清楚,曲线进入饱和状态之后的部分非常平坦,而SiC MOSFET的分界点则没那么明显,即使进入饱和状态,电流曲线仍有一定斜率的上升。

典型的IGBT输出特性曲线(左)与SiC MOSFET输出特性曲线(右)

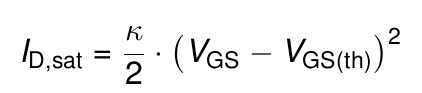

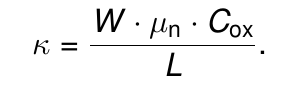

由于SiC-MOS器件的VGS(th)随着漏极电压的增加而减少,饱和电流ID,sat上升得更明显,原因可参见以下公式,可以看到,饱和电流与过驱动电压(VGS-VGSth)的平方成正比。

其中k为一个常数

W-沟道宽度,µn-电子迁移率,Cox–栅氧化层电容,L–沟道长度

对系统进行短路保护设计必须考虑DIBL的影响。例如,我们需要知道直流母线电压下的退饱和电流水平。在器件设计中,可以通过更有效的p-屏蔽结构和更长的沟道来减少DIBL效应。然而,这两个参数也可能导致更高的RDS,on。

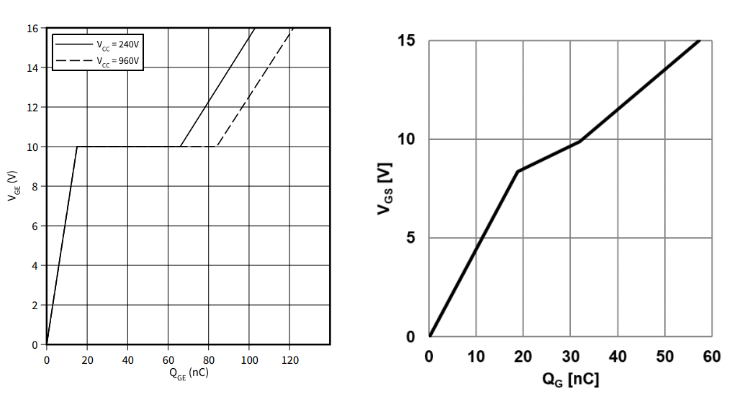

DIBL的第二个效应可以通过图3中的栅极电荷曲线来观察。VDS变化期间的VGS是一个斜坡,而IGBT的典型栅极电荷曲线,这时是一个恒定的VGS值。

栅极电荷曲线对比:IGBT与SiC MOSFET

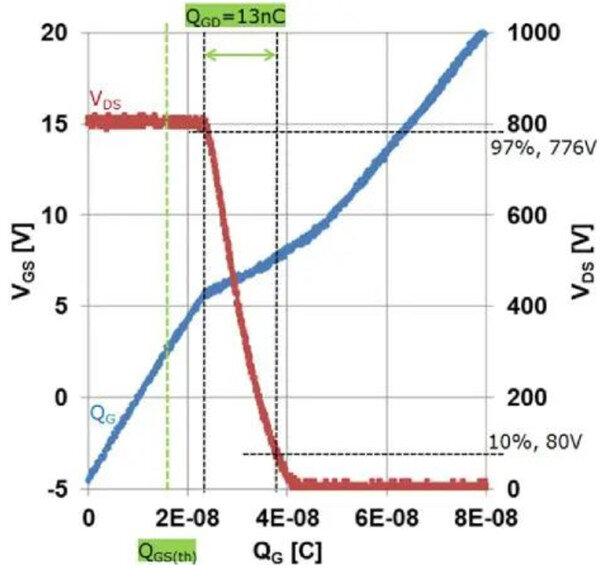

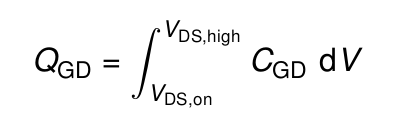

因此,在计算重要参数QGD时,使用斜坡时间段是不正确的。更合适的方法是将VDS波形与QG特性叠加在同一张图上,并如图3所示设置取值范围(取10%VDS~97%VDS)。

图3:英飞凌45mΩ/1200V芯片的栅极电荷特性(蓝色),在800V、20A、25°C、VGS-5V→15V的情况下,开通时测量,利用VDS(红色)波形提取QGD

这其实是在对测得的小信号电容CGD进行积分。

上述方法可得45mΩ器件QGD为13nC。从图3中还可以提取使VGS达到阈值水平所需的电荷(QGS,th,约18nC),可以发现QGD/QGS,th之比小于1。这有助于抑制寄生导通,即在VDS快速变化的情况下,通过CGD给栅极充电的电荷量,小于使栅极电压VGS抬升至阈值VGSth的电荷量。

总结一下,商业化的SiC MOSFET普遍采用短沟道设计,用来降低导通电阻,这使得DIBL(漏致势垒降低效应)比较明显。买电子元器件现货上唯样商城。SiC MOSFET中的DIBL效应首先表现在饱和电流随VDS上升而上升,其次表现在栅极电荷曲线中的米勒平台段呈斜线。从图中计算得出SiC的QGD需要将VDS与栅极电荷曲线叠加在一起,通过限定边界条件的方式得出。

来源:英飞凌,赵佳

/4

/4

文章评论(0条评论)

登录后参与讨论