芯片遍布生活中的各个角落,在一些领域对芯片的制程是有很大要求的。比如智能手机产品,市面上的高端旗舰手机几乎都搭载5nm,4nm制程的处理器。

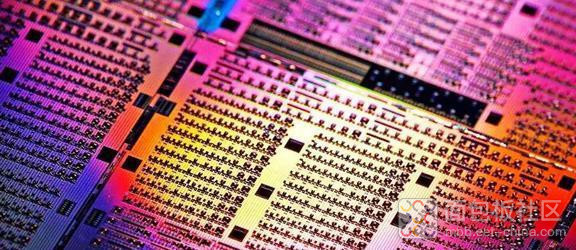

指甲盖大小的芯片就能集成上百亿根晶体管,在有限的手机主板面积中发挥强劲的性能表现。由于手机主板面积非常宝贵,所以要想提升芯片的性能,在同样的芯片尺寸范围内,只能提高芯片制程工艺,增大晶体管密度,让芯片容纳更多的晶体管。

只是未来的芯片制程会越来越难突破,而且成本也会增加。那么有没有既能节约成本,又能确保芯片性能提升的方式呢?

或许先进封装是一个方向。用先进的封装技术来改变芯片搭载,布控方式。行业内探索的“芯粒”“芯片堆叠”等技术其实都是先进封装的一种。而根据形式类别的不同,会分为平面的2D和立体的3D封装技术。

台积电已经在大力探索先进封装,并帮助客户成功造出全球首颗3D封装芯片。大致来看,台积电是帮助名为Graphcore的厂商生产出IPU芯片,芯片的名称为“Bow”。

Bow单个封装芯片中集成了600亿根晶体管,而且采用的是7nm工艺制程。如果是传统的单颗芯片,7nm能集成几十亿根晶体管已经很不容易了,可以说是突破7nm极限了。

就算是5nm制程,市面上主流的芯片也仅仅集成一百多亿根晶体管。能做到600亿根晶体管的密度,完全得益于先进封装技术的支持。

那么这是怎样的芯片封装技术呢?其实使用的是台积电SoIC-WoW技术,通过将两颗裸片上下叠加,上面的裸片负责供电和节能,下面的裸片保障运算和处理。在两颗裸片的3D封装效果下,性能叠加,算力和吞吐量都有所提升。

/4

/4

文章评论(0条评论)

登录后参与讨论