GaN垂直器件作为下一代电力电子器件的绝佳解决方案,其可靠性作为关键核心一直是业内比较关注的问题。现从优化漂移区、电荷捕获等进行探讨。

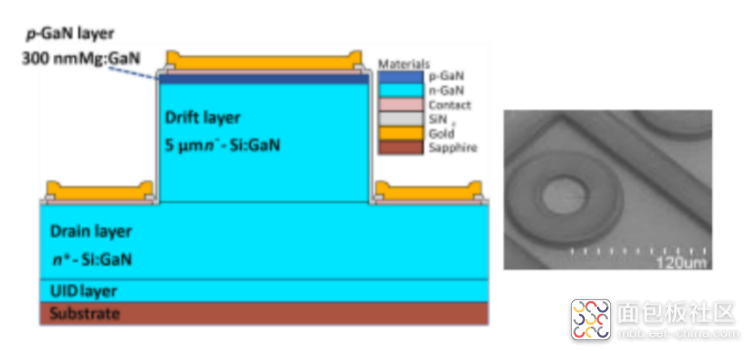

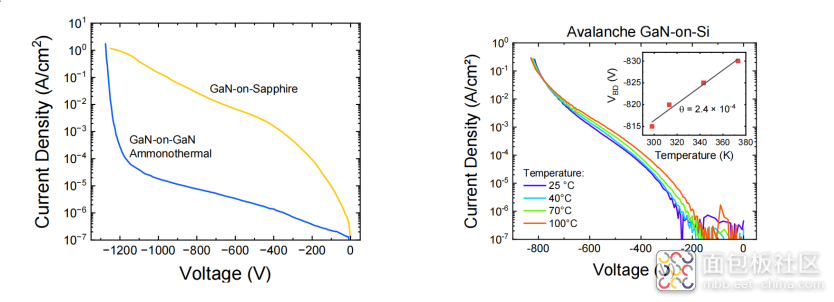

垂直GaN器件的性能在很大程度上取决于漂移区的特性。降低非故意意杂质浓度有利于提高迁移率,对于高残余碳(C:1017cm-3),迁移率低至 20cm2/Vs)的,而对于更高质量的材料,则有报道称其迁移率值约为 960cm2/Vs,可与碳化硅的迁移率相媲美。漂移区的残余电导率也会限制为防止过大漏电流而施加到堆栈上的最大电压。为了研究这个问题,在GaN衬底上生长了厚度为 10 µm 的漂移层(在 pn 结中),掺杂水平约为8 E15cm-3;这种结构的击穿电压可达 1200V 以上,即与碳化硅器件的电压范围兼容。

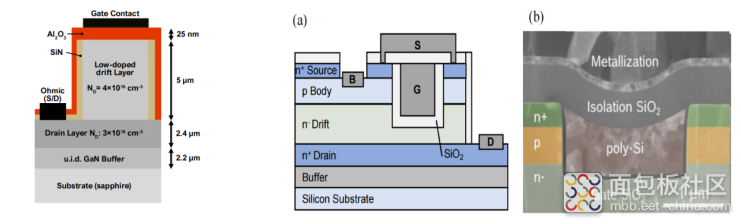

与垂直GaN-on-GaN相比,GaN on Sapphire这可能会导致更高的漏电流(见图中蓝宝石衬底上的数据),最近在硅基氮化镓伪垂直 pn 二极管中演示了近千伏的雪崩能力,这是可靠运行的必要特性(存在于硅和碳化硅器件中)。

对于GaN垂直器件来说,垂直电流也是一个必要条件,以尽量减少寄生效应和电流拥挤效应。如果使用的是同质外延衬底,可通过在晶片底部直接沉积金属来实现,对于异质外延衬底,可通过在晶体管区域下方局部移除衬底来实现。典型的工艺是蚀刻(用于硅衬底)或激光剥离(用于蓝宝石衬底)。

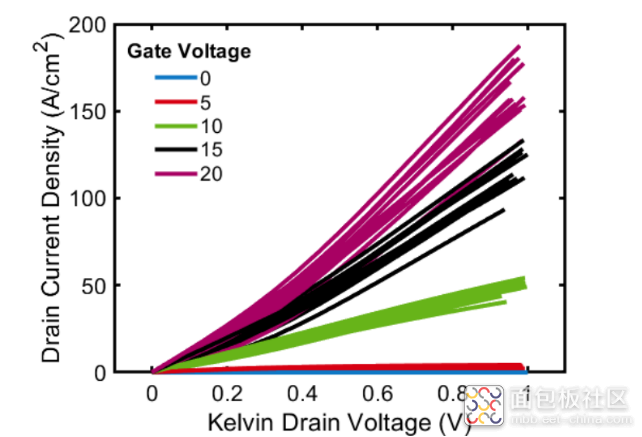

下图显示了由此产生的结构以及器件和 ID-VD 曲线;为确保高导电性,使用了钛/铝背面触点,并用铜金属化加固。

SiC器件在正栅极应力作用下可能会出现显著的阈值电压偏移(0.5V-1V)典型的过程包括(边界/界面态的电子捕获)冲击电离引起的空穴捕获。

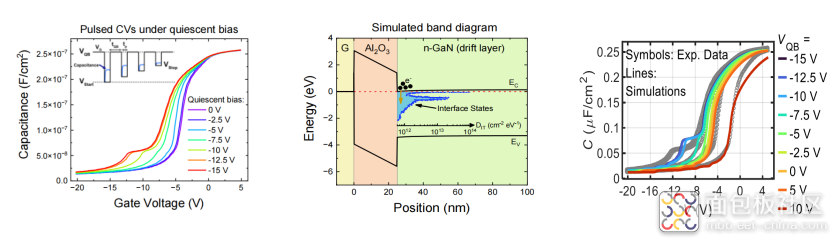

为了研究GaN垂直 MOS 结构中阈值不稳定性的物理根源,我们对准垂直 MOS 电容器和 MOSFET进行了广泛分析,并考虑了两种不同的电介质(Al2O3和SiO2)。

对 MOS 电容器(Al2O3 电介质)进行的脉冲电容-电压(C-V)分析表明,存在正(PBTI)和负(NBTI)阈值不稳定性,C-V 曲线中存在特征性 “驼峰”。通过快速 CV 测量对界面陷阱密度进行了实验推断,结果表明以 EC-0.6 eV 为中心存在一个深电平峰。得到的陷阱分布被输入到 TCAD 模拟中,结果与实验数据非常吻合。C-V 曲线中的驼峰是由于费米级在电荷分布峰值对应的能量处被钉住。

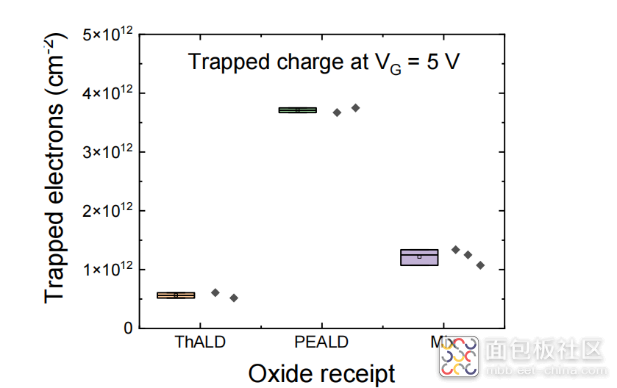

为了确定 Al2O3 沉积的最佳条件,我们进行了进一步的实验。结果表明,与等离子体增强 ALD(PEALD)相比,热 ALD(ThALD)获得的 CV 滞后较低。然而,由于 ThALD 的稳健性可能有限,混合(ThALD/PEALD)堆栈被认为是最有希望用于 Al2O3 垂直 FET 的沉积工艺。

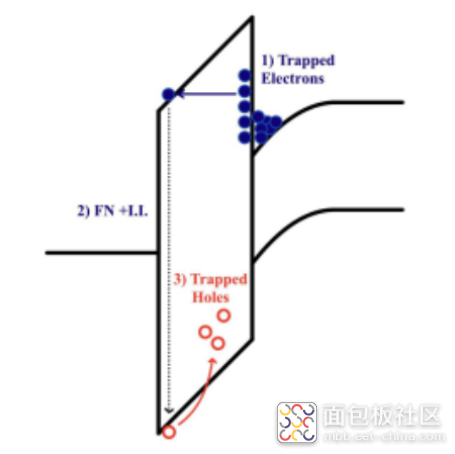

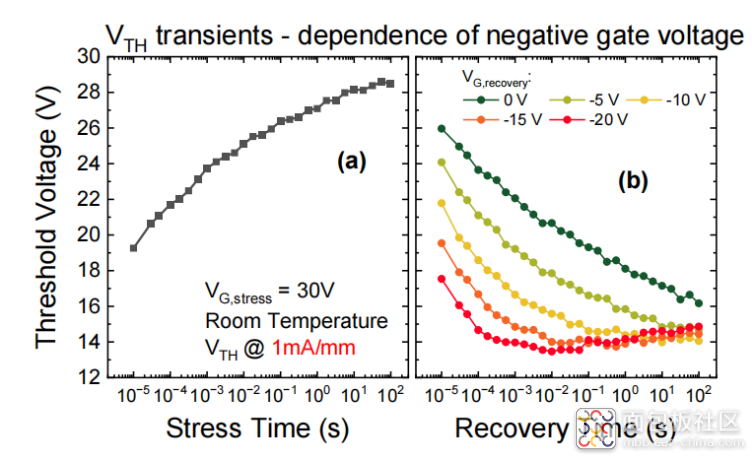

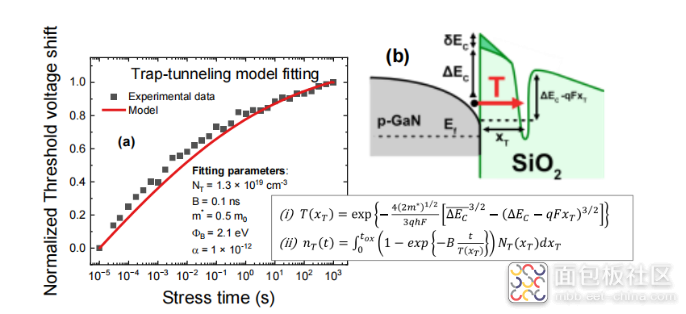

关于 MOSFET(使用二氧化硅电介质)中的电荷捕获,发现第一代器件在正栅极应力的作用下,阈值电压会出现明显的正移。

考虑到沟道电子向氧化硅陷阱态的隧穿,可以提出一个数学模型来解释动力学。通过考虑隧穿概率和计算陷波电荷积分,我们能够准确地再现实验数据,模型保持一致。我们还进行了 TCAD 模拟,以研究边界(BT)和界面(IT)陷阱的作用。对陷阱分布进行了校准,同时考虑了带隙上半部分的供体和 EC 附近狭窄分布的受体。

结果表明,栅极电压越高,电子从沟道到 BT 的隧穿概率越高,阈值电压也随之变化。新一代器件显示电子捕获大大减少。从器件A到器件B的重大改进是通过改变 SiO2沉积工艺实现的,从785 ℃的低压 CVD(LPCVD)和800 ℃的 PDA,到 880 ℃的LPCVD和900 ℃的PDA。

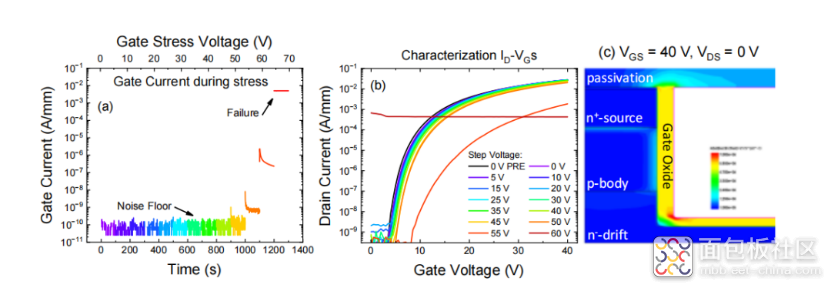

失效过程一系列栅极和漏极阶跃应力实验评估了GaN垂直器件的可靠性。在栅极阶跃应力期间,在具有 70 nm SiO2 栅极电介质的器件上,发现栅极电流在 VG=45 V 时可以忽略不计;在更高的电压水平上,载流子通过氧化物注入导致漏电流增加,直到在 VG=60 V 时失效。在碳化硅器件上进行的类似实验表明,载流子通过 Fowler-Nordheim 隧道从半导体注入栅极的作用很大。暴露在较高的栅极电压下可能会导致电子在氧化物中捕获,从而使阈值电压发生正向移动并与之进行比较,发现碳化硅器件的失效电压与其类似。观察到的失效过程归因于栅极绝缘体的击穿;在垂直 FET 中,由于电场的拥挤,沟槽角可能是有利的失效点。

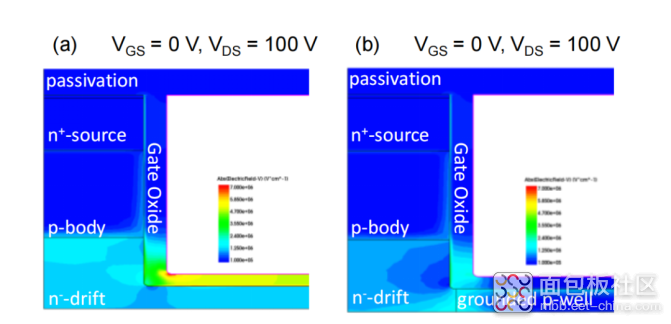

此外,在栅极接地、漏极电压较高的漏极应力情况下,氧化物中的电场可能接近电介质的击穿场强。下图显示了模拟结果(VG=0 V,VD=100 V),表明电场超过6 MV/cm。与碳化硅器件的比较表明,管理沟槽两侧和底部的电场是确保高离态可靠性的关键步骤。人们提出了各种解决方案,包括底部厚氧化物、双沟槽结构、双p基底结构和底部保护p阱。此类解决方案也正在对氮化镓垂直场效应晶体管进行初步探索(即使氮化镓的区域选择性p型掺杂不如碳化硅成熟):下图显示了一个例子,与对碳化硅所做的类似,沟槽底部(标记为 “p-阱”)放置了一个 p 型屏蔽,以显著降低关态条件下电介质上的场强。

关键的电荷捕获过程已被识别和建模,针对 Al2O3 和 SiO2 电介质提出了将阈值电压不稳定性降至最低的解决方案。针对栅极和漏极应力,确定并描述了垂直氮化镓器件的主要失效过程。

/4

/4

文章评论(0条评论)

登录后参与讨论