沙特阿拉伯的阿卜杜拉国王科技大学(KAUST)报道了利用原子层刻蚀(ALE)技术改善富铝III族氮化物(III-N)肖特基势垒二极管(SBDs)性能的研究成果 [Tingang Liu et al, Appl. Phys. Lett., v126, p152109, 2025]。特别指出的是,使用ALE技术制造的AlGaN SBDs展示了高达1205V的击穿电压,而未经ALE处理的SBDs击穿电压仅为308V。

该团队称:“通过减少界面陷阱和消除自然氧化层,ALE技术可以降低漏电流,使肖特基势垒更加均匀。”

与镓(Ga)等金属相比,铝(Al)的氧化速率更快,因此在AlGaN半导体的金属有机化学气相沉积(MOCVD)外延结构中,通常会使用GaN帽层来保护下层材料免受氧化。

KAUST团队解释说:“在AlGaN材料中,自然氧化层通常厚度约为1-3纳米。过厚的氧化层很可能是由于高密度的缺陷造成的,这使得表面更容易被氧化。而缺陷表面层是在MOCVD生长过程结束后的腔室冷却阶段形成的,此时腔室内残留的金属有机源会促使其在较低温度下持续生长。”

在金属触点快速热退火等工艺中,缺陷层往往会助长不必要的氧化。ALE工艺能够降低表面缺陷密度,从而减少后续制造步骤中的氧化。ALE还能去除富铝材料暴露在空气中时形成的任何自然氧化层。

通过去除氧化层、缺陷层,KAUST团队希望为“提升基于AlGaN的功率器件在下一代高压应用中的性能和可靠性”指明方向。

研究人员介绍了这种技术的优势:“原子层刻蚀(ALE)技术是一种以原子级精度去除材料的刻蚀策略。与通常在高射频功率(通常超过300W)下操作的传统反应离子刻蚀(RIE)不同,等离子体ALE通常在特定的化学处理后,以较低的离子能量(约10eV)和较低的速率温和地去除材料。这种自限制过程使得ALE能够实现精确的厚度控制和最小的表面损伤。”

增加III族氮化物半导体材料中的铝含量,应能将其带隙从GaN的3.4eV提升至接近AlN的6.2eV。更宽的带隙与更高的击穿临界电场相关,这将能在更小的结构中实现高电压,满足功率处理器件的需求。通过减少表面缺陷,ALE技术可以提高场效应晶体管和 p-n 二极管等其他功率器件类型的性能。

研究人员使用了2英寸的AlN/蓝宝石模板,通过MOCVD先生长出500nm的1300℃AlN外延层,随后生长了200nm的1150℃硅掺杂Al0.86Ga0.14N层。AlN模板层厚度为1μm。根据X射线分析,外延层中的螺位错和刃位错密度分别估计为2.79x10⁷/cm²和3.41x10⁸/cm²。

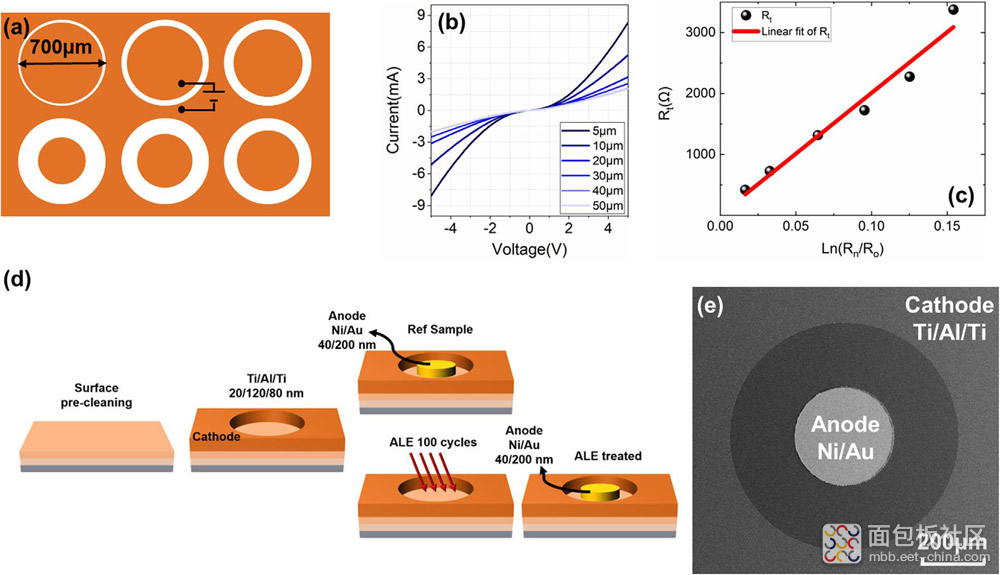

该团队用激光从外延材料上切割下来的1cm×1cm样品上制造了SBDs(图1)。在制造前,样品先用硫酸/过氧化氢混合溶液清洗,再用由氢氟酸和氟化铵溶液组成的缓冲氧化物刻蚀剂清洗。团队解释说:“这些清洗步骤旨在消除激光切割过程中产生的杂质,并去除样品表面的大部分污染物。”

图1:(a) CTLM图形示意图。(b) 和 (c) CTLM测量结果及用于计算接触电阻率的线性拟合。(d) 参考样品和经ALE处理样品的制造流程;红色箭头指示处理位置。(e) 所制造器件的扫描电子显微镜(SEM)视图。

为了评估欧姆接触的接触电阻率,研究人员使用经过图案化和退火处理的溅射钛/铝/钛(Ti/Al/Ti)金属叠层制作了圆形传输线测量(CTLM)结构。接触电阻率约为2.01x10⁵ Ω-cm²。霍尔测量显示,AlGaN层的方块电阻、载流子浓度和迁移率分别为421kΩ/□、4.3x1016 /cm³ 和 17.4cm²/V-s。

SBDs的欧姆金属阴极与CTLM结构中使用的相同。镍/金肖特基阳极则分别在有或没有 ALE处理的情况下沉积。未经ALE处理的SBD作为参考样品。肖特基金属通过电子束蒸发沉积。

ALE工艺使用牛津仪器(Oxford Instruments)的设备进行。刻蚀循环包括:氯气注入(0.03秒),吹扫(10秒),刻蚀(5秒),以及间隔(0.4秒)。该循环重复100次,根据原子力显微镜(AFM)测量,估计刻蚀深度为10nm。SBD的阳极直径为300μm,与阴极的间距为200μm。

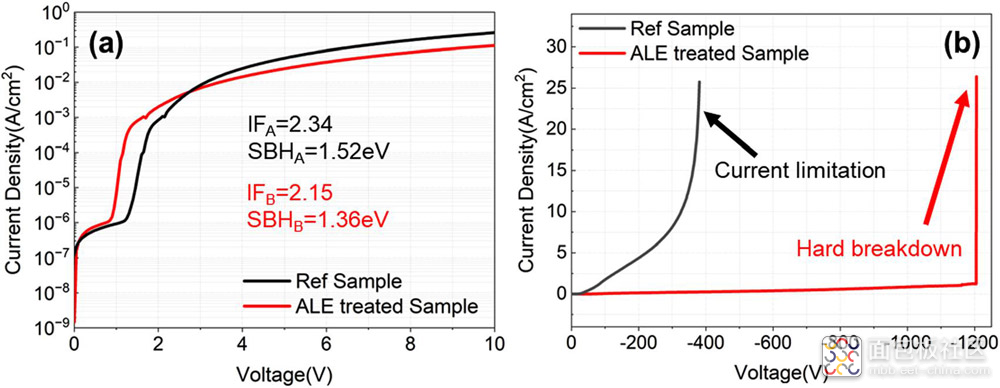

图2:(a) 参考样品和经ALE处理样品的正向电流-电压(I-V)特性。(b) 反向电流-电压(I-V)特性。

经过ALE处理的SBD和参考样品的开/关电流比均为106(图2)。测量点为开启状态10V,关闭状态-5V。经ALE处理的SBD的理想因子为2.15,而参考样品为2.34。ALE处理和参考样品的肖特基势垒高度分别为1.36eV和1.52eV。电容-电压(C-V)测量结果显示,ALE样品的势垒高度更高,为4.85eV,参考样品为5.05eV。

研究人员称:“C-V测量的肖特基势垒高度(SBH)与I-V测量的SBH之间的差异,可能分别源于参考样品表面氧化层中高密度界面态,以及ALE处理过的样品表面等离子体化学过程诱导的界面态。ALE提高了SBDs的理想因子,但导致肖特基势垒高度略有降低。”

器件的击穿特性差异显著:参考样品为308V,而经ALE处理的SBD为1205V。此外,击穿模式也不同:参考样品突破了漏电流限制,而ALE处理的SBD则发生了突然的硬击穿。

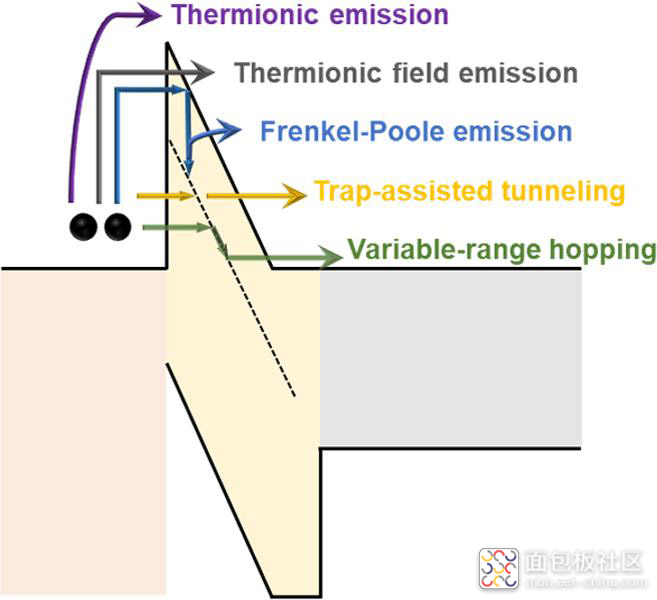

图3:通过肖特基势垒的电流流动和击穿机制。

研究人员利用温度变化测量来分析漏电流和击穿机制(图3)。尽管经ALE处理的SBD相比参考样品具有更好的反向偏置性能,但其漏电流的大小仍然过高,不能归因于热电子或热电场发射效应。研究团队认为,导致载流子通过陷阱辅助隧穿(TAT)或变程跳跃(VRH)偷偷穿过势垒的原因是缺陷辅助传导,而不是传统的电极限制传导。温度分析表明,与参考样品相比,TAT对ALE处理的SBD中的影响较小。而VRH分量在两种器件类型中被认为是相当的。团队得出结论,ALE处理主要改善了高电场载流子的传输性能。

文章来源:https://www.semiconductor-today.com/news_items/2025/apr/kaust-250425.shtml

论文链接:https://doi.org/10.1063/5.0251499

周子吉编译整理

/4

/4

文章评论(0条评论)

登录后参与讨论