tziang@hotmail.com

2012-10-18

TI有与ADI对应的ADC,分别是ADS8556/85578558,精度和通道数相同,只是采样率更高,

软硬件完全相同,这里的讨论应该也同样适用于TI的ADC芯片

原理性部分:

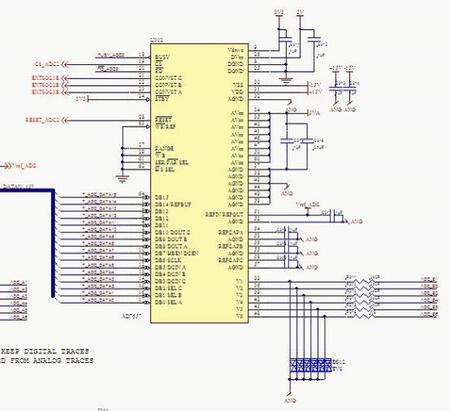

1)电源的去耦电容偏少,容量偏小,尤其是AVcc,根据规格书第22页,每个供电脚都需要一个10uF和0.1uF的电容并联去耦;

2)CS_N直接连到BGA芯片,调试很不方便,可以考虑增加测试点;

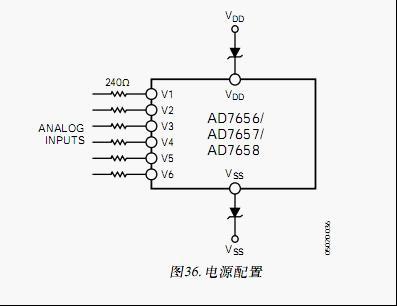

3)根据规格书第29页,三种情况:a)模拟信号调理电路电源不同于Vdd,Vss;b)模拟输入在Vdd,Vss建立之前注入芯片;c)AVcc先于Vdd,Vss之前施加,需要串接二极管和电阻保护

关于第3点,调试时,AVcc先于Vdd和Vss之前施加,导致烧毁了4片AD7657

PCB部分

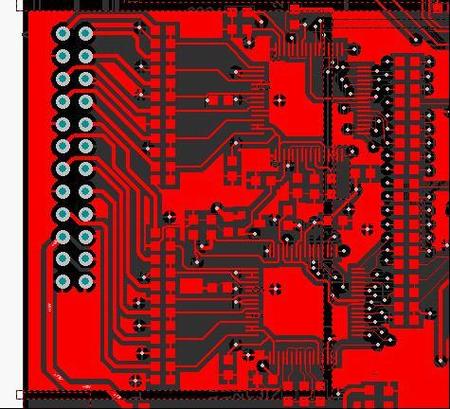

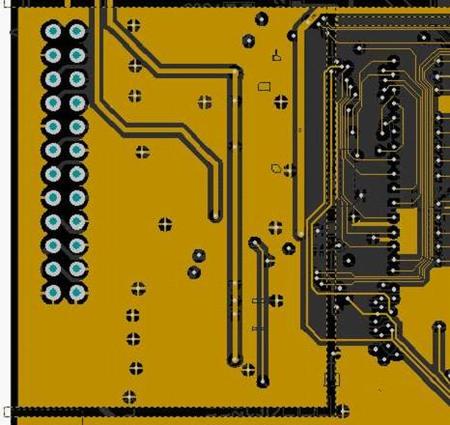

AD芯片Top层和第2层下面有部分走线,BUSY,RD_N和几根DATA信号

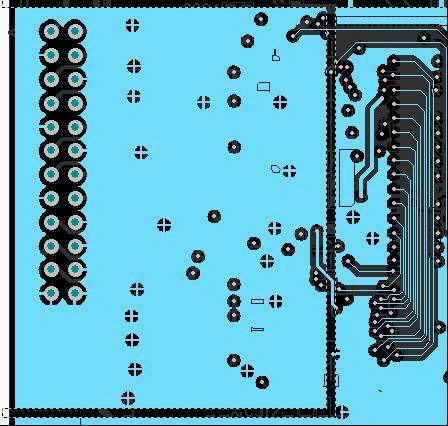

TOP层

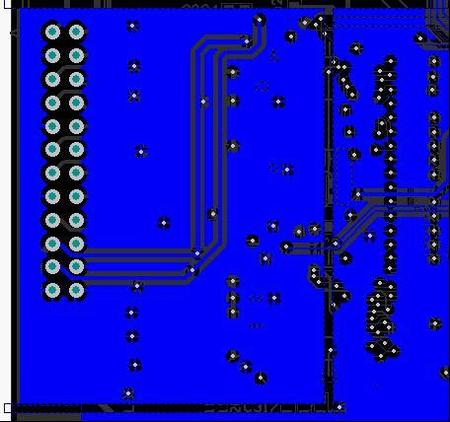

L2层

L3层

BOTTOM层

对照根据规格书第29页,

1)模拟数字地分割,单点连接,符合要求;

2)避免在器件下方走数字信号线,否则噪声将耦合至芯片,top层和第二层的数字信号走线需要调整;

3)CONVST等时钟信号需要使用数字地保护,这点没有重视,下板需要修改;

4)退耦电容的选择,尤其是6个AVcc,可以分成3对,AD7656每对使用100uF,AD7657每对使用33uF,AD7658每对使用22uF,根据ADI推荐,下板使用退耦要求低的AD7657-1版本。

补充,关于SAR ADC的支持电路说明

1)基准电压,通常要使用输出阻抗低的缓冲式基准,基准电压电路的动态部分基本上是一RLC储能电路,R位于ADC内部(一些串联开关电阻),C为基准电压储能或去耦电容,L为基准电压本身的电感。如果使用电感高得多(比好的缓冲式基准电压高100倍以上)的低功耗基准电压,将导致RLC电路处于欠阻尼状态,引起AD的粘连为现象。

2)ADC芯片REF上的大电容,REF上的电容不是旁路电容,是SAR ADC的一部分,但又不适合放在硅上。REF的电容是ADC位判断期间用来补充内部CDAC的电荷,从而与内部电容阵列上的电荷一起平衡比较器。随着二进制位加权过程的向前进行,将从此电容中不断提取少量电荷。储能电容大小不足也会引起粘连位问题。

详细内容参考ADI 的应用文档-AN-931.

/4

/4

文章评论(0条评论)

登录后参与讨论