专题二:加法器

加法运算在FPGA设计中经常使用,其中常用的加法器有全加器和半加器,一个基本的N位二进制加法可由N个全加器构成,每个加法器的表达式如下:

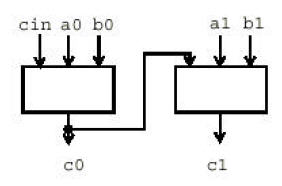

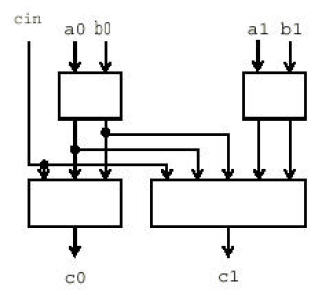

由上式可得进位c的逻辑相比于加法结果位s逻辑较复杂,因此设计延迟较短的进位逻辑成了关键,目前有很多进位相关技术,如串行进位、超前进位等。如图1所示为串行进位方式的加法器,图2所示为超前进位方式的加法器。

图1

串行进位相应Verilog HDL代码:

assign c0=(a0 & b0) | ((a0 | b0) & cin);

assign c1=(a1 & b1) | ((a1 | b1) & c0);

图2

超前进位相应Verilog HDL代码:

assign p0 <= a0 | b0;

assign g0 <= a0 & b0;

assign p1 <= a1 | b1;

assign g1 <= a1 & b1;

assign c0 <= g0 | (p0 & cin);

assign c1 <= g1 | (p1 & g0) | (p1 & p0 & cin);

按速度和面积原则,串行进位以面积为原则,而超前进位以速度为原则。

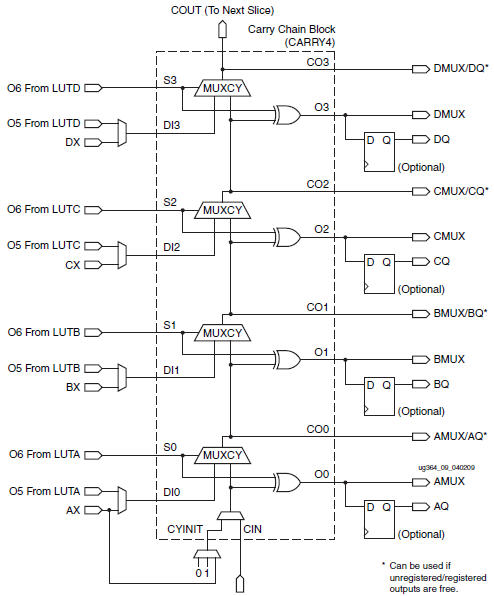

加法器几乎是每个FPGA设计中必备的,因此专门为加法器设计一个快速的进位链是很有必要的,实际上FPGA厂商也是这么做的,以Xilinx 7系列FPGA为例。如图3所示为其Slice中的进位链结构,在Xilinx 7系列FPGA使用之CLB探索中介绍过在CLB中有2个Slice,而每个Slice中有4个LUT,LUT有2个输出:O6和O5,图3中Slice中进位链为每个LUT分配了一个选择器MUX和异或门XOR构成的进位逻辑,并且4个从下到上纵向排列;CIN为下端进位输入,COUT输出给上端的进位,用于连接多个Slice间的进位,这样就保证实现位宽加大的加法器也能快速进位。

图3

FPGA中有了专用的快速进位链,在编写代码时就无需采用如超前进位这样的方式了,可采用常规的全加器进位结构,如下代码所示为16位加法器:

module adder_test(

input clk,

input rst,

input [15:0] a,

input [15:0] b,

input ci,

output reg [15:0] sum,

output reg co

);

always@(posedge clk)

if(rst)

begin

co<=1'b0;

sum<=16'd0;

end

else

{co,sum}<=a + b + ci;

endmodule

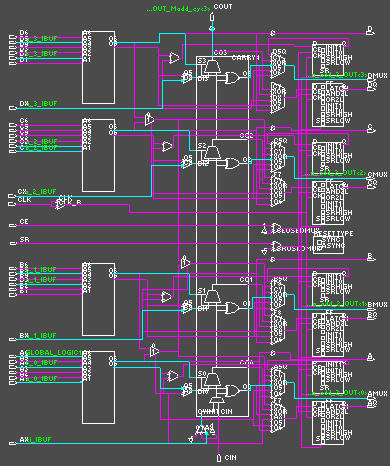

经过综合、实现后,在Xilinx FPGA Editer工具中可以查看加法器的具体布线图,如图4、5所示,由图4可得15位加法器可由4个Slice实现,每个Slice实现4个全加器,2个Slice间用一条进位链连接;而其它进位都在Slice里面,如图5所示,由一个LUT和为其分配地MUX、XOR进位结构就可实现一个全加器。

图4

图5

通过Post-Map Static Timing分析得到Min period limit: 1.408ns (710.227MHz) (Tbcper_I(Fmax)),其中进位逻辑延时非常之小,主要的布线延迟都在I/O和逻辑之间。

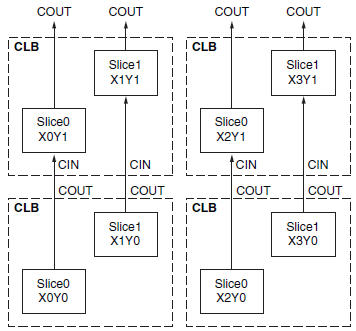

另外从图4仔细观察可以发现在蓝色Slice旁还有一个灰色的Slice未使用,此灰色Slice是与蓝色Slice同在一个CLB中的另一个Slice,为什么会有这种结构?这还是因为CLB的结构,上文中说过在一个Slice内部进位链是纵向的,而在Slice外部如图6所示,也是纵向的,同处于一个CLB中的2个横向排列的Slice并没有进位链,这样就保证了所有进位链统一的纵向性,是进位链延时达到最小。

图6

/4

/4

Hoki 2012-4-1 23:18

在程序中正常使用加法或者比较之类的操作,XST综合器就能自动综合出快速进位链

用户1660450 2012-4-1 14:57

Hoki 2012-3-28 13:42

用户615011 2012-3-27 13:39