之前有写过一篇说的是理论。现在我举一两个PCB截图进行简单的说明。这些只是我个人的理解,如果有什么不妥的地方,欢迎各位网友指出,大家共同学习和进步。

首先,我说一下分地的问题。一般来说,PCB的地主要分为数字地,模拟地,电源地。分完之后呢,单点进行连接。可以直接连接,效果好点的可以通过磁珠和0欧电阻。下图是一个直接单点连接的图片:

左边的那小部分是模拟地,右边大的部分是数字地,她们是单点连接。为什么要分地呢?因为模拟地很敏感,它要求必须干净,而数字地有很多噪声,如果不分,模拟地可能就全部被污染了。理论上说你能分地最好,但是当你的PCB面积很小并且很密集的时候,分地就很困难了。像AD芯片这样的,模拟地和数字地在同一个芯片的不同管脚,分的特别零散。还有时钟地也必须独立。电源地就更不用说了,最大的干扰源,敏感的地要离的远远的。一般我的做法是:表层这些地都不相连,自己的是自己的地,不跟其他相连,打地孔到主地,主地面积大,吸收能量强,所以不分。这样所有的地可以在主地相连。

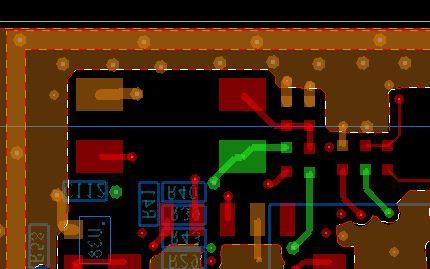

以下是一个PCB截图:

我们在画PCB的时候,尤其是电源部分要参考datasheet主的推荐画,一般都是电源的输入和输出地要连在一起,以便很好的回流。信号地和电源地分开,而且不同电源的地不要画在一起,比方说3.3V和1.8V芯片的地不要在表层相连。过大电流的mos管的地画大点,打地孔散热。电源脚的feedback,要从输出电容采样,而不是从芯片的输出脚。这样调整的更精准些。打地孔和电源孔的时候要注意计算孔的过流能力,孔太少不行,孔太多的话会把铜皮打穿,孔打的时候不要太整齐,很容易把铜皮打穿。

在这里,我想说下时钟晶振的地的画法:

整个晶振表层的地都掏空不铺铜,也不用表层的其他地相连,只引出一个地线,打地孔到主地。内层的地要铺铜。

另外还有,在给一些敏感线包地的时候,注意头尾要加地孔,而且地线很长的时候要隔一段打一个地孔。地线至少要0.2mm以上,太细的地线和太长的地线而不隔一段打孔,不能起到隔离的作用,反而成了干扰源,还不如不包,让信号线远离其他线。

最后,我想提一点的是,自动铺完铜后,要把一些锐角和直角,一些小面积的地铜皮挖掉,如下图绿色圆圈所示:

这些可能成为天线,而对其他信号进行干扰。

最后,我说下PCB的叠成结构,这很重要。一般信号都要有参考地,参考地干净与否会影响到信号的准确性;电源层能和一个地层相邻,以便更好的回流,尤其是走大电流的情况下,更需要地的完整性。拿一个6层板,理论上最好的分法是:1信号2地3电源4信号5地6信号。敏感的信号走内层,不要穿过电源的电感,电源内层的铺铜也不要穿过这些敏感的信号线。相邻层不要平行走线。太晚了,就说到这里,其他的部分就参考前篇的理论,在琢磨琢磨。最近碰到比较郁闷的是,功放5V在发射的时候,大电流,把总电和其他电源瞬间拉下很多,只有靠加330uf以上的大电容解决,可是板子空间有限,因此我们在设计的时候,还是要考虑在电源的输入和输出多加大电容。切记。

/4

/4

文章评论(0条评论)

登录后参与讨论