历时一个月,总算将ARM9--S3C2440A 的核心板+底板,绘制完毕。今天刚发出去打样,特意让工厂做上15片,到时可以免费送10片。估计下周便可回来。这是小弟我绘制的第5代学习板了。中间所经历和收获的“非自己亲历亲为,不能明白”!和我一样有DIY兴趣的朋友不要错过哦!

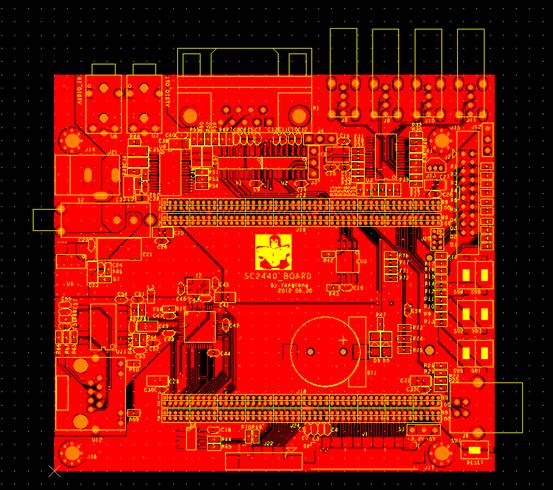

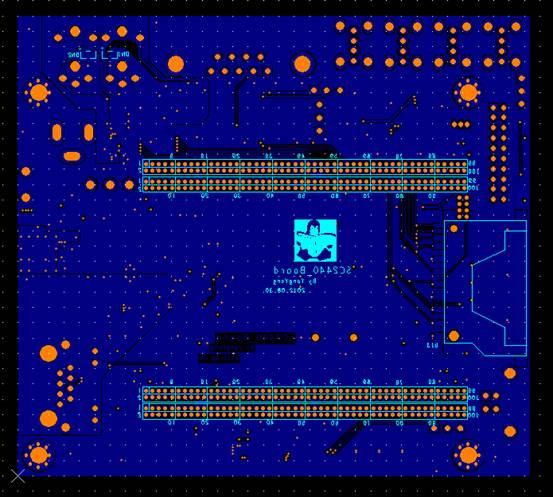

核心板和底板都采用四层板。保证电源,信号完整性。核心板尺寸为65MM*45MM*1.6MM, 底板尺寸为100MM×90MM×1.6MM。

200PIN 1.27插针引出所以能用的IO.底板再次引出200PIN,不怕需要用的管脚却未引出。

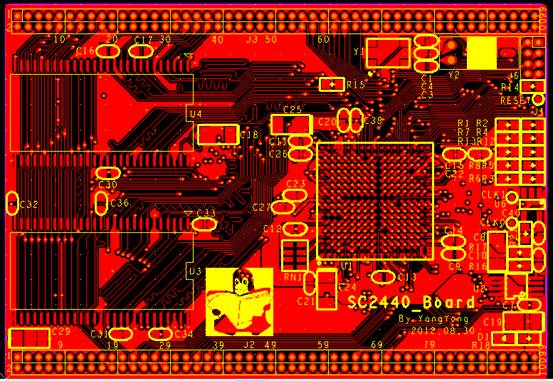

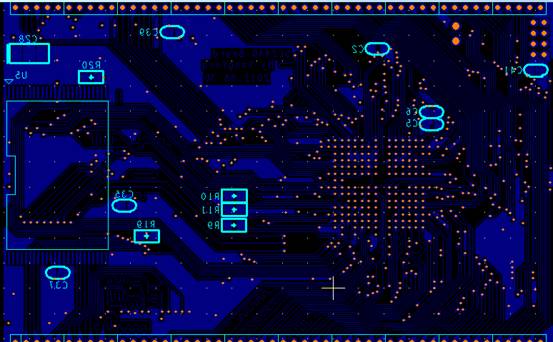

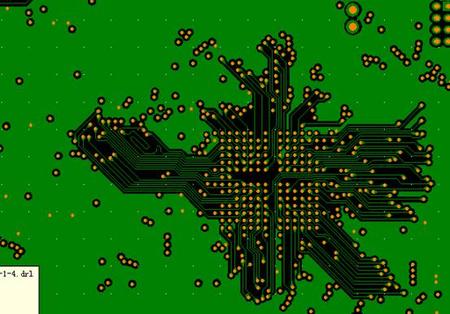

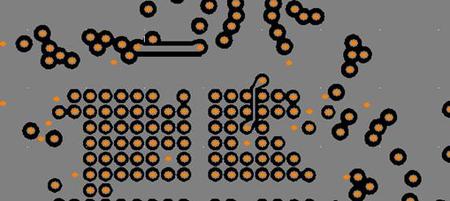

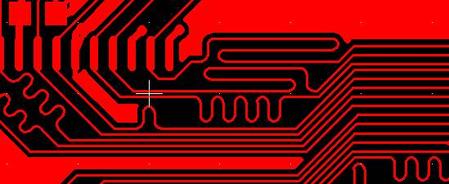

以下是光绘图片,后续等板子焊好,调试OK后会补上板子的实际图片。。。。。。。。。。。。

避免博主多次贴图,请您到博主日志浏览。。。。。。。。。。

http://bbs.ednchina.com/BLOG_ARTICLE_3007215.HTM

+++++++++++++++++++++++++++++++++++++++++++++++

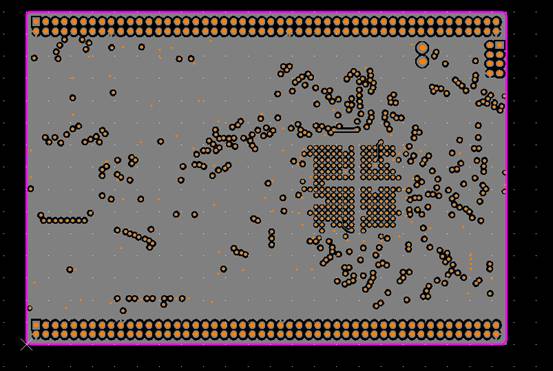

保证地平面的完整性

核心板

底板

需要提供给PCB厂家的15个光绘文件,最好附上你的层叠结构,免得那边的工程师打电话问你要怎样的层叠结构。

///2012.09.10 等了一个多星期,还没拿到板,居然告诉我板子做废了,得重新做,周四才到手,哎!。。。。

趁此闲余之际,粗略概述一下我在画板中的一些原则吧。。。。。

1 退耦电容尽量靠近芯片电源管脚,能有多近,就靠多近,过孔出线如下图

2 各种线,尽量是直线,能少拐一个弯的,不拐两个弯。尽量在一层走线,能钻一个孔的,绝不钻两个孔。

3 尽量在顶层,和底层走除电源和地线在外的所有线,走不下,可以少量再电源层走线,越少越好。理论上来讲,地线层绝不走线。但迫不得已,可以非常短的走几条线。但距离绝对不能太长。而且还不能造成地平面被分割的情况出现。

VCC层

地线层

4 至于阻抗匹配问题。我个人认为能少一个弧度的,就少一个,尽量拉长每个蛇线的长度,这样能减少信号反射。蛇线采用3倍线宽的间距。

5 所有退耦电容引出线,就近过孔到电源层或地线层

以上几点,纯属小弟一家之言,希望不会误人子弟。。。。。。。。

//////2012.12.05 板子已经回来两个月了,但手头上事情比较多,一直未能有精力去焊接,等忙完这阵子腾出手来接续本文。谢谢!

用户927376 2013-3-1 12:32

用户425516 2013-1-16 21:52

用户432432 2013-1-15 10:05

用户498106 2012-12-27 13:23

用户425516 2012-9-1 15:37

用户498106 2012-8-31 21:39

用户425516 2012-8-31 16:45

博客居然升级了???感动中。。。。再接再厉。。。。

用户425516 2012-8-31 16:43

用户403664 2012-8-31 16:34

用户425516 2012-8-31 16:21