2.2多采样率处理(信号的抽取与插值)

本设计中,从1K的采样序列中,输出512、256、128采样序列时,需要做抽取操作。信号的抽取可能会出现频谱的混叠,我们必须保证混叠不影响到带内信号。

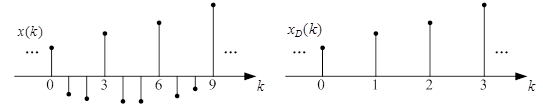

(a)原序列 (b) 3倍抽取后的序列

图2.10离散序列的抽取

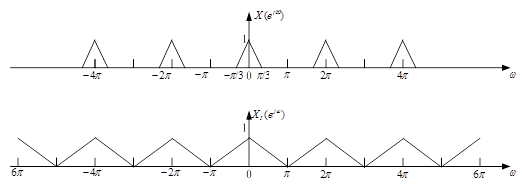

抽取后信号的频谱变化如下:

(1)没有发生混叠的情况:

图2.11原序列的频谱和3倍抽取后序列的频谱

(2)发生混叠的情况:

图2.12发生混叠的情况

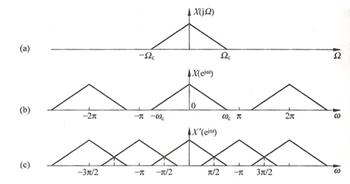

这种情况,在抽取前必须滤波,数字滤波器的截止频率小于[-π/M, π/M],M为抽取倍数,进过此滤波器的数字序列再进行抽取,就不会发生频率混叠了。此滤波器叫做抗混叠滤波器。

转换的模拟域滤波器,必须满足此关系:

![]() :抽取的结果不会发生频谱混叠

:抽取的结果不会发生频谱混叠

其中fs为原序列的采样频率,fc为抗混叠滤波器的截止频率。

图2.13先滤后抽的频谱变化

从上面分析得出以下结论:

1、 一个设计中原始信号的通带频率fpass是固定的,所以必须保证fpass;<>

2、 fc 离fpass越远越有利于滤波器的设计(滚降越小);

3、 混叠是可以产生的,只要保证折叠到低频部分在fpass之外,带来的坏处是带外衰减不足;

4、 分级抽取有益于滤波器的设计。

/5

/5

文章评论(0条评论)

登录后参与讨论