基于FPGA的数字滤波设计—FIR设计1

3.1 FIR阶数和系数的确定

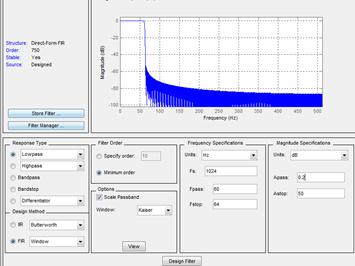

按照1.3节给出的滤波器指标,利用MATLAB的FDATOOL工具,采用窗函数法设计出的FIR滤波器需要700多阶,如图3.1所示。评估FPGA资源,不能够完成滤波的主要原因是无法保存输入的历史数据。即使参数做微调也只能将阶数降到300阶。究其FIR阶数居高不下的原因主要在于,60Hz-64Hz的过渡带相对于采用频率1KHz来说太窄,即滤波器的滚降过快。Fstop=64Hz就是由此![]() 公式计算得来。从1024序列中抽取出128的序列,那么M=8,计算得fc<64Hz。所以为了保证不出现混叠,Fstop=64Hz。

公式计算得来。从1024序列中抽取出128的序列,那么M=8,计算得fc<64Hz。所以为了保证不出现混叠,Fstop=64Hz。

经过多次评估得出,在2C8器件基础上对72个通道进行FIR滤波,最多只能运算85阶,为了便于计算采用64阶FIR滤波。

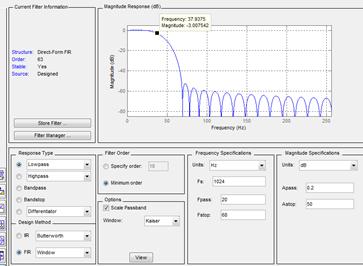

考虑到脑电信号一般低于30Hz,那么我们将通带频率定为20Hz。同时我们考虑到,混叠只要对带内信号不产生影响,混叠也可以产生,那么我们可以计算出Fstop=128-60=68。这样优化的方向就是,使得滤波器的过渡带趋于平坦,我们知道,过渡带直接影响到FIR的阶数。

形成了新的指标如下:

原采样率 :Fs=1024Hz

通带 :Fpass=20Hz 保证30Hz衰减不低于3dB

截止频率 :Fstop=68Hz

利用MATLAB的FADTool工具生成FIR模型如3.2图所示。37Hz左右才衰减3dB,保证率30Hz不衰减3dB。

具体设置参数如下:

选择:低通(lowpass)、FIR、基于窗口设计(window)、kaiser窗口设计。

设置:采样频率Fs=1024,通带Fpass=20,阻带Fstop=68;

通带衰减Apass=0.2,阻带衰减Astop=50dB。

这些参数中,Fpass、Fstop、Astop等都可以修改,主要目的就是为了使得FIR的阶数为64阶(由于FPGA硬件资源限制,本系统中只能设计64阶的FIR)。当然在保证系统需求的前提下,可以尽量降低FIR的阶数。

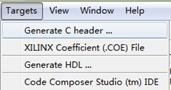

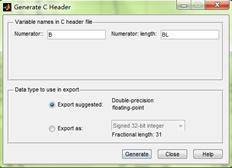

FIR阶数确定后,就可以生成FIR系数了,利用FDATOOL如图3.3的系数生成工具,可以生成各种不同类型的系数。

图3.3 FDATOOL系数生成工具

此系统中FPGA采用了16位有符号乘法器结构,所以在此生成了Signed 16-bit integer类型的系数。

3.2 基于FPGA的72通道FIR滤波器设计

3.2.1 FIR参数和FPGA资源之间的对应关系

1、 FIR的阶数决定了FPGA乘法单元使用次数,阶数的高低影响滤波的效果(频响)。

2、 FIR计算的位宽选择:8bits 、16bits、32bits。影响精度,即滤波效果(小信号)。

3、 运算速度,决定了FPGA的主时钟,即影响功耗。

4、 通道数量,每个ADC器件采集的24路信号轮流滤波,那么滤波过程中需要保存每个通道的阶数个历史数据,影响的存储单元容量的大小。

3.2.2 FIR实现结构:1个MAC对应一个ADC器件

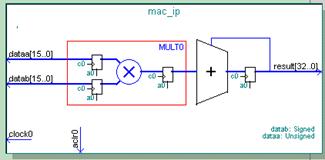

利用Quartus II软件中的MegaWizard Plug-In Manager工具生成的MAC单元结构如图3.4所示。设置datab为有符号输入(输入FIR系数),dataa为无符号输入(输入信号序列)。aclr0为异步清零。

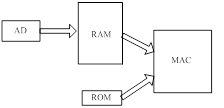

利用此MAC单元设计出的64阶FIR滤波器结构如图3.5所示。ADC器件对24路通道进行采样,并将采集到的16bits位宽的数据存入RAM中。在RAM中划分24个通道对应的不同的地址范围。RAM中保存的每个通道输入的历史数据个数有FIR阶数决定,即为64个。在ADC完成当前通道当前采样值后,MAC单元开始从RAM中调入数据、从ROM中调入FIR系数,进行FIR最基本的乘累加运算,运算次数由阶数决定。系数采用16bis无符号整型表示,所以在计算完成后需要做归一化处理。

/5

/5

用户1605975 2013-11-10 22:00