脉动阵列(Systolic Array)计算有限冲激响应(FIR)

综合软件:QuartusII 12.1

仿真软件:Modelsim-Altera

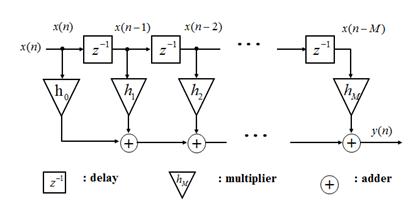

FIR:有限脉冲响应滤波器。有限说明其脉冲响应是有限的。

FIR计算公式:

![]()

硬件实现结构:

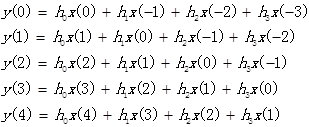

4阶FIR计算公式:

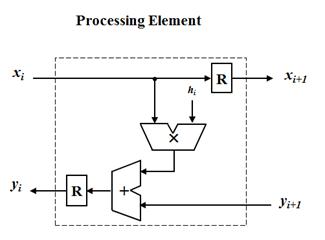

最小计算单元(PE):乘加单元

+ : adder 加法器

Î : multiplier 乘法器

R : register 寄存器

hi : coefficient 系数

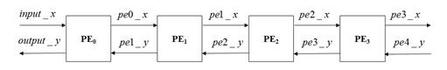

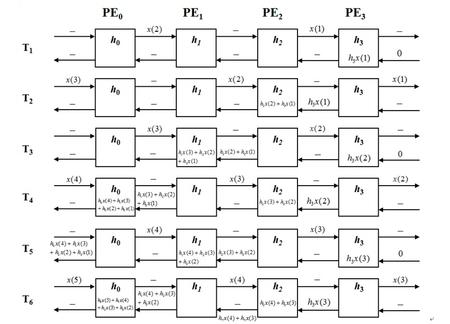

利用脉动阵列结构级联PE,来完成4阶FIR的计算:

注意:pe4_y=0;

数据流图:

注意:

1、 CLK每隔一个时钟,输入一个X的值;

2、 T1时刻以前,已经有过2个CLK令x1传递到PE2中;

3、 从X1进入后CLK的上升沿的输出的是X1点的FIR值,因为之前的计算中已经保留了后三项的乘积和;

4、 控制好输入X和时钟的流水,可以让整个硬件一直处于有效的流水输出状态。

5、 流水状态下,输入是隔一个时钟更新数据的,那么输出也是隔一个CLK有个一正确的输出。

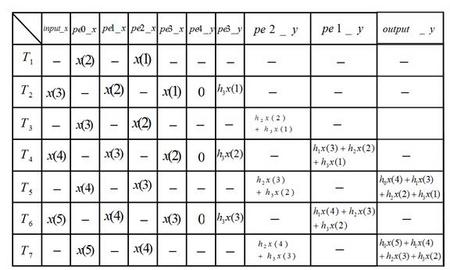

计算单元中的两个寄存器值如下:(具体值,可以参照纸质笔记)

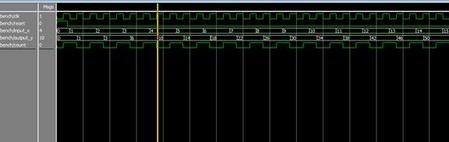

时序仿真图如下:

令四个系数都为1,那么等价于,输出Y是当前输入X和之前的三个输入X-1,X-2,X-3之和。流水形成后,每个X输入下一个CLK上升沿总有对应的Y输出。

同时必须,每两个CLK输入一个新的X值。

也就是说,计算频率必须为输入频率的两倍。

/2

/2

文章评论(0条评论)

登录后参与讨论