脉动阵列(Systolic Array)计算矩阵乘法(Array Multiplication)

下一个目标是实现流水线输出,提升硬件资源的利用率。

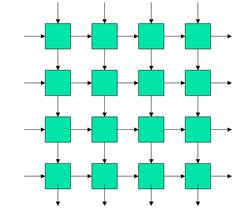

脉动阵列(Systolic Array):数据流同步流过相邻的二维阵列单元的处理器结构,一般不同方向流过不同数据。

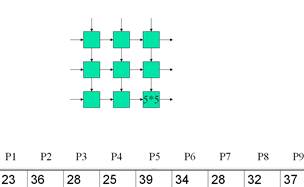

结构:

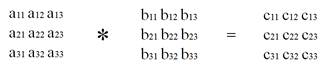

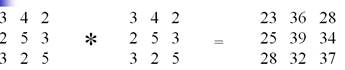

矩阵计算:

C语言描述每个输出矩阵中的值:

For I = 1 to N

For J = 1 to N

For K = 1 to N

C[I,J] = C[I,J] + A[J,K] * B[K,J];

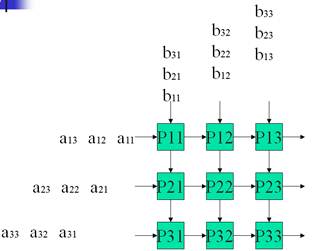

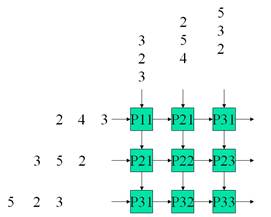

运用N x N processing units,输入数据呈批次输入:

二维不同数据在同一时钟下依次输入每个处理单元,而后完成乘法并存在其寄存器中。

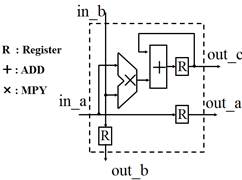

其中每个PE(处理单元)结构如下:

是一个乘加单元 c=c+(a*b)

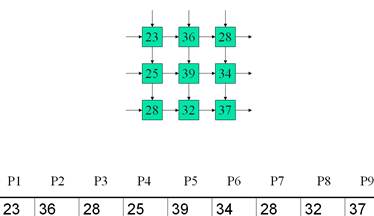

例子:计算两个3×3矩阵的乘积

结构:

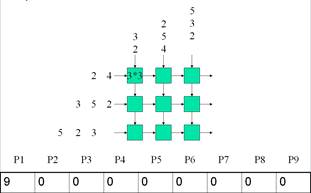

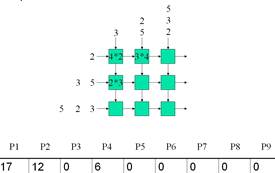

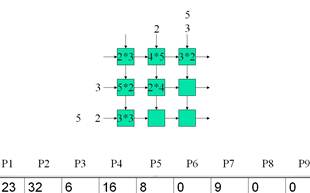

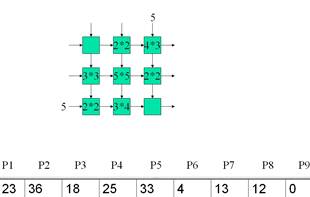

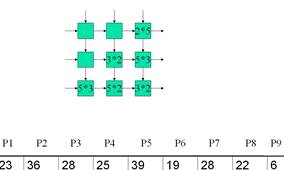

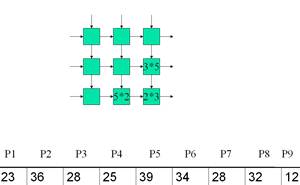

在CLK驱动下的每一个步骤如下:

Clk1:

Clk2:

Clk3:

Clk4:

Clk5:

Clk6:

Clk7:

Clk8:输出

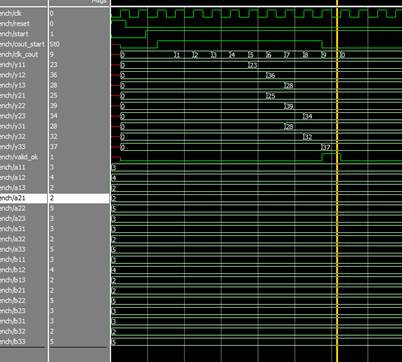

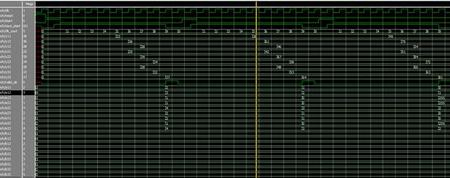

功能仿真图:

在start 上升沿到来后的第一个CLK上升沿开始计数

Count_start高电平期间

Cout=1时,准备a11和b11;

Cout=2时,将数据打入寄存器,并计数出a11*b11;

Cout=3时,计数a11*b11+a12*b21

Cout=4时,计数a11*b11+a12*b21+a13*b31

Cout=5时,用寄存器打一拍输出Y11。

其他类似。

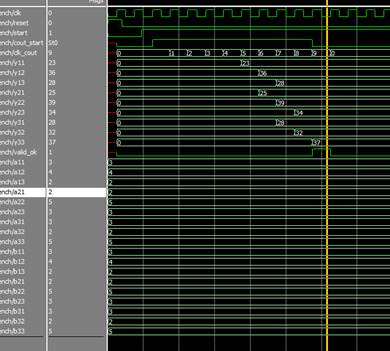

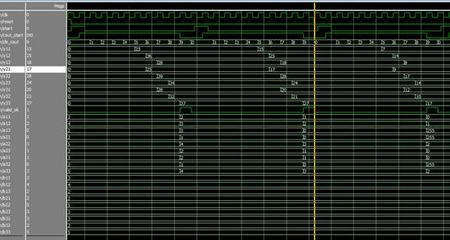

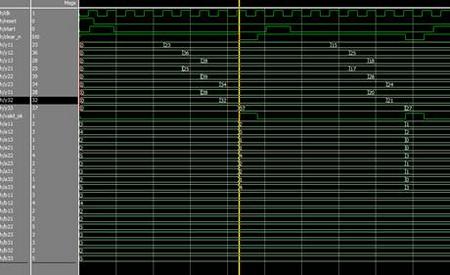

时序仿真图:

连续运算,中间忘了将乘加单元寄存器清零的情况,功能仿真:

每次计算出结果后清零寄存器,修改后的功能仿真图:

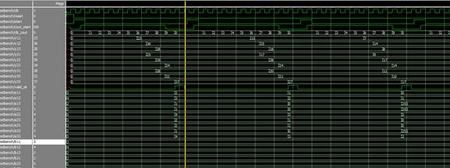

数据在送入运算单元之前,采用寄存器打一拍,功能仿真图:

状态机便于实现控制。

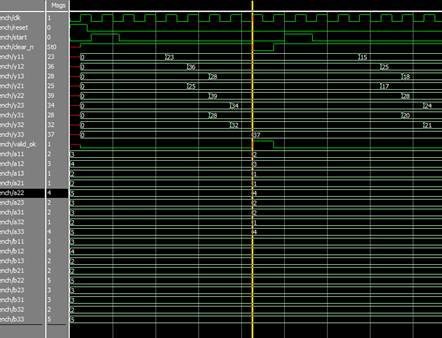

状态机控制:功能仿真

时序仿真图:

/2

/2

用户377235 2016-3-8 20:45

用户403664 2013-7-5 15:23