Verilog-FPGA硬件电路设计之三——关于迟滞信号

在条件选择语句中,由于信号的处理存在时间上的差异,从前级传递到下级的数据就存在到达时间先后的问题,因此为了提高电路的速度,对迟滞信号要安排在当前单元最后处理,也就是放在本级靠近输出的位置。

1、if语句条件分支中的判断信号迟滞

在之前的文章中介绍了if语句的优先级和生成硬件电路的关系,自然对于迟滞信号的处理,当然是放在优先级比较高的if分支中,下面两个例子可以对此作说明。

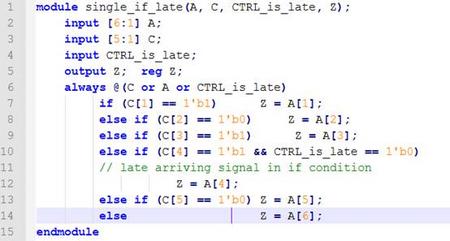

1.1 迟滞信号放在最低优先级的if分支中

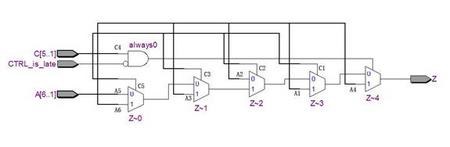

RTL图:

RTL图:

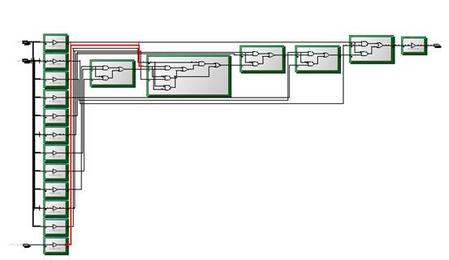

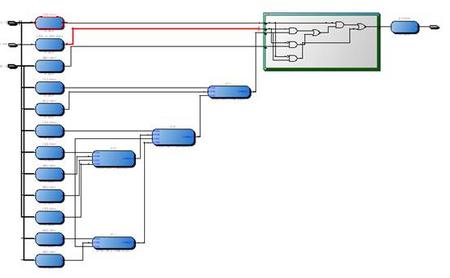

Tec 图:红线是迟滞信号

从RTL图和Tec图都可以看出迟滞信号在本级的前部分就被处理了。这样很容易因为信号的迟滞而处理的并非有效信号。

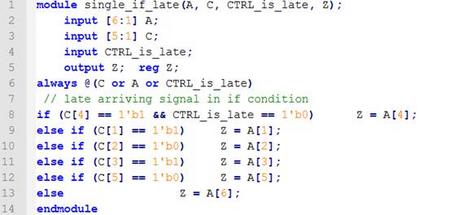

1.2 利益if语句的优先级对迟滞信号进行处理

RTL图:

RTL图:

Tec图,红线是迟滞信号

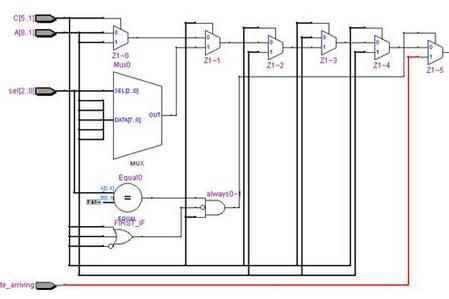

可以看出如果输入有迟滞信号输出,应该将其放在第一个if语句中,让其靠近输出端,减小延时。

2、if-case嵌套语句中,case内部有迟滞信号

在文章“Verilog-FPGA硬件电路设计之二——if语句和case语句的区别”中的case内部存在着迟滞信号。对于case 分支的输入 DATA_is_late_arriving 迟滞信号,怎么将其从case分支中提出来呢?就是说,如果将case分支中的语句从case中提取处理,并且将其向后移。

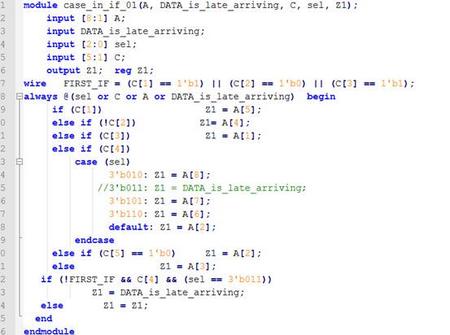

可以先来看看优化后的代码:

说明:

说明:

1、always块中有两个if分支结构,按照“Verilog-FPGA硬件电路设计之一——if语句优先级”所说,第二个if的优先级高于第一个if(因为always块中是顺序执行的)。所以我们将 DATA_is_late_arriving 单独放在一个if的分支结构中,并将其放在最高优先级中,靠近电路的输出。

2、最后的else Z1 = Z1; 此句可以注释掉,但不能将其改成Z1 = 0;或者Z1 = 1; 因为,改了之后,else就实际包括了第1个if的所有判断情况,那么自然,第一个if就被阻塞掉了。关于组合逻辑电路中, 一个always块中包含两个以上的if分支结构,并且都对同一个信号操作,且都包含有else分支时,要注意被阻塞的情况。

RTL图:

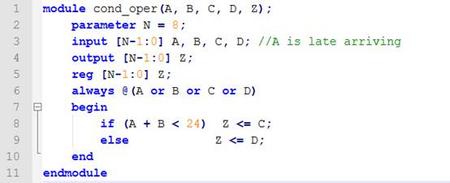

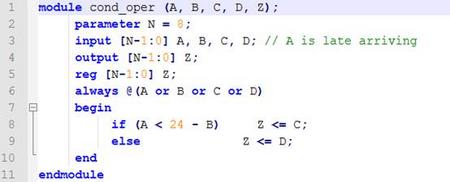

3、if语句的条件表达中包含有操作符

优化

/1

/1

用户379288 2013-10-28 16:44

用户441844 2013-6-25 08:26