Verilog-FPGA硬件电路设计之二——if语句和case语句的区别

一个if语句中嵌套了case语句的例子,可以很好的看出if语句和case语句的区别。

module case_in_if_01(A, DATA_is_late_arriving, C, sel, Z);

input [8:1] A;

input DATA_is_late_arriving;

input [2:0] sel;

input [5:1] C;

output Z; reg Z;

always @ (sel or C or A or DATA_is_late_arriving)

if (C[1]) Z = A[5];

else if (!C[2]) Z = A[4];

else if (C[3]) Z = A[1];

else if (C[4])

case (sel)

3'b010: Z = A[8];

3'b011: Z = DATA_is_late_arriving;

3'b101: Z = A[7];

3'b110: Z = A[6];

default: Z = A[2];

endcase

else if (!C[5]) Z = A[2];

else Z = A[3];

endmodule

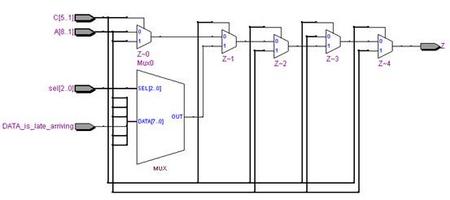

从此电路,可以看出 case 和if 在组合逻辑电路中的区别:

case 语句,通常case中的选项(sel) 不是1bit信号(如果是1bit用if判断更为方便),也就是说分支非常的多,而且各个分支语句没有优先级,所以硬件电路会生成一个多bits的MUX单元。

而if语句,因为有优先级,所以只能每个if语句生成一个1bit的mux单元,每个mux单元从前到后有优先级的级联。注意:最靠近输出端的优先级最高。

/3

/3

文章评论(0条评论)

登录后参与讨论