综合软件:QuartusII 12.1

仿真软件:Modelsim-Altera

1、输出done无寄存器,直接从组合逻辑电路输出

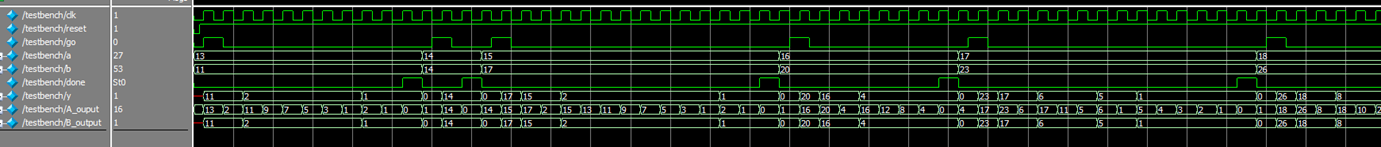

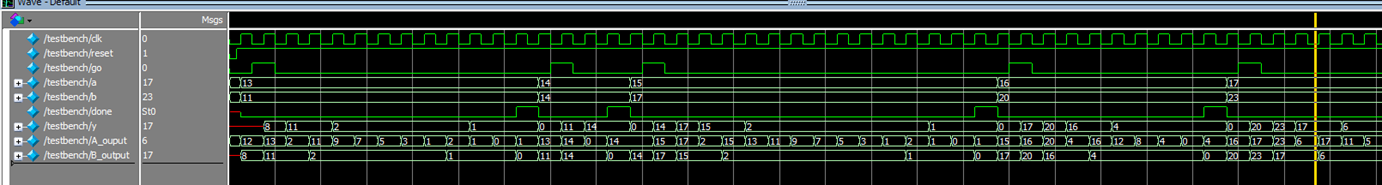

1.1功能仿真

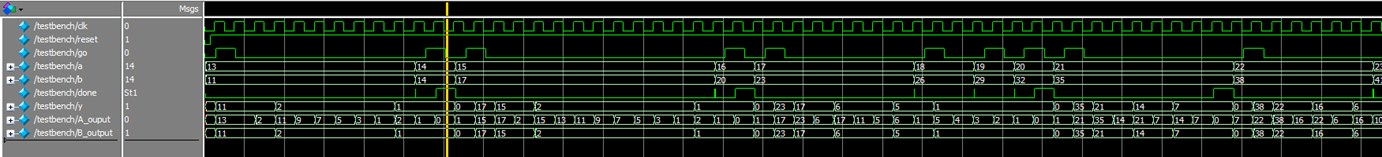

1.2时序仿真:存在竞争冒险的输出

可以明显的看出存在着竞争冒险。在testbench中,我们在检测到done的下降沿时更新输入值a,b。然后有时候,done出现了冒险,更新了值,但此时上一次的输入还没有计算出最大公约数,那么此次更新的值,就不能被运算单元所接受(状态机此时没有回到IDEL状态,无法接受新值)。从而没法计算出新输出值的最大公约数。

2、延时一个CLK输出

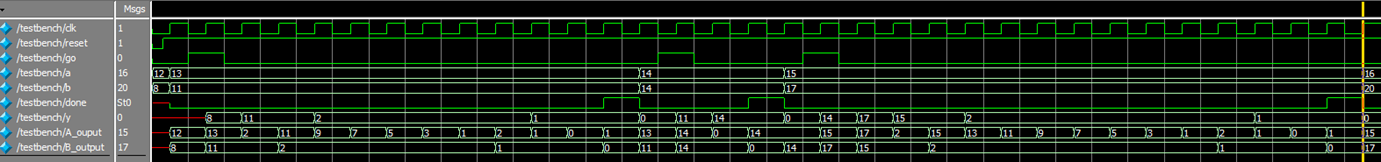

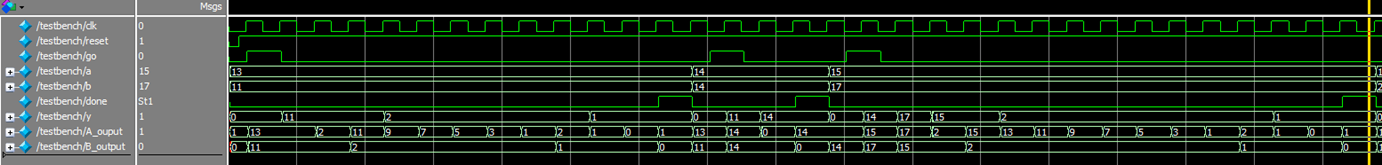

2.1 功能仿真(检验不出门延时和线延时):

和上面的功能仿真相比,可以很明显的看出,此时需要多一个CLK的时钟,才能输出有些值

2.2 时序仿真: 利用寄存器打一拍,可以消除竞争

出现一个问题:复位完成后, datapath中的 A寄存器(对于图中的A_output)就等于0了,CLK上升沿到来时,直接判断有输出,令done=1, 输出值Y=B=0;

所以必须在复位时令A!=0;

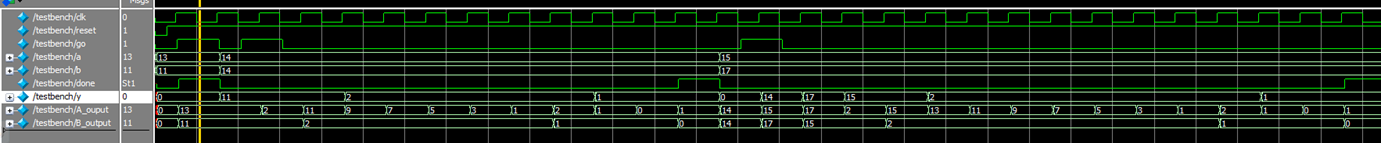

做出修改后的

功能仿真图:

时序仿真图:

可以看出, 修改后,功能仿真没有变动。但时序仿真中,一开头不会再出现误判断,和误输出。

/2

/2

文章评论(0条评论)

登录后参与讨论