(接上篇)

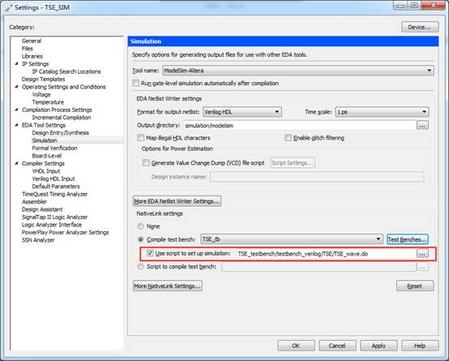

编译完成后,一般不会出现错误,这时候,就可以通过设置NativeLink来将Quartus II工程文件与Modelsim-Altera软件关联起来了。设置NaitveLink的详细步骤如下图所示:

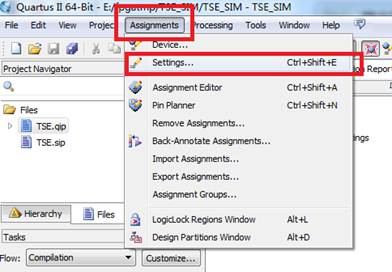

点击Assignments—>Settings

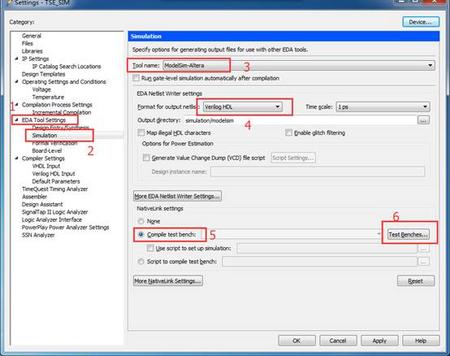

在弹出的对话框中(如下图所示)选择EDA Tool Settings(红框1处),选择Simulation(红框2处),核对红框3处和4处是否与图上设置的一致,然后勾选红框5处的Compile test bench,点击红框6处的Test Benches以进入新的testbench设置窗口。

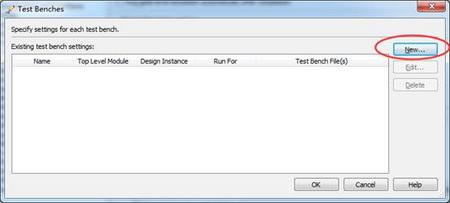

在新的testbench设置窗口中,点击New以创建一个新的Testbench设置脚本,如下图所示:

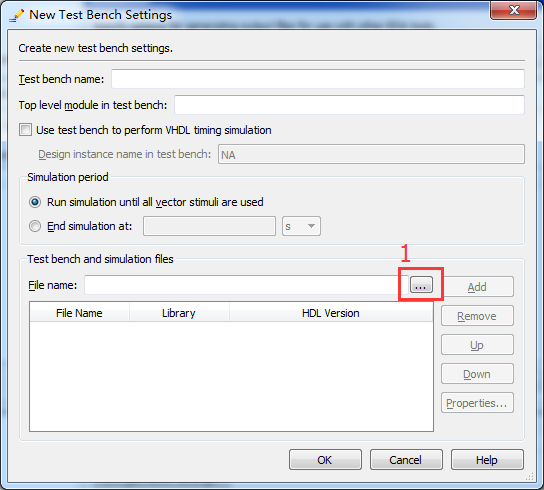

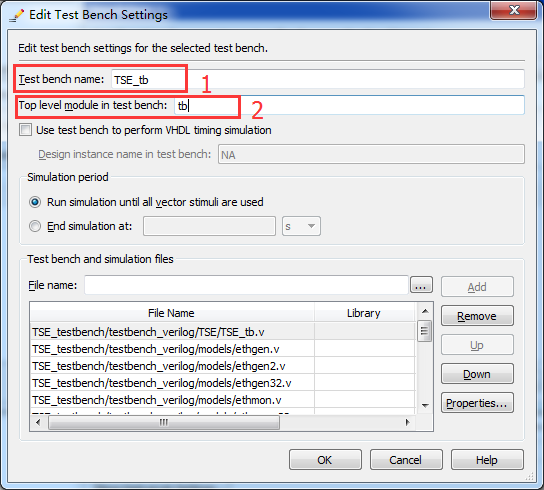

单击New Test Bench Settings选项卡中的File name一栏最右侧的三个小点(红框1处所示):

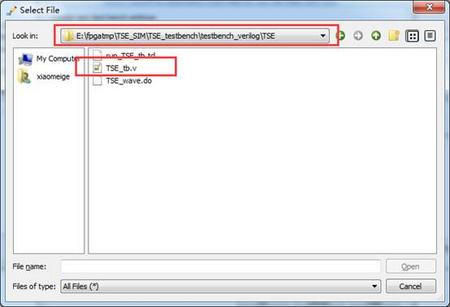

在弹出的文件选项卡中,将目录定位到工程目录下的

” <IP名>_testbench/testbench_verilog/<IP名>”

目录下,选择<IP名>_tb.V文件并Open(如下图所示),返回到New Test Bench Settings选项卡中。

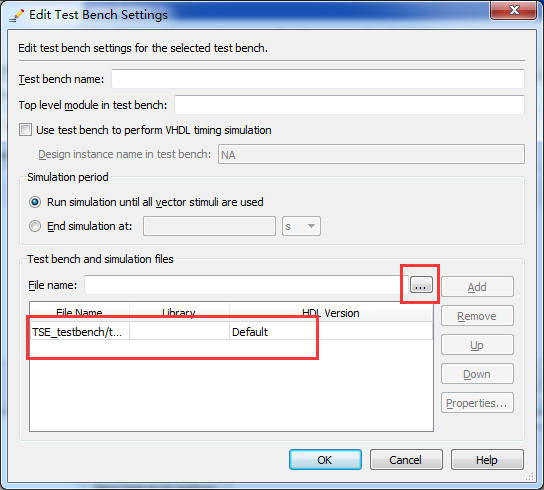

点击Add将<IP名>_tb.v添加进去,然后再次点击那三个小点(如下图所示):

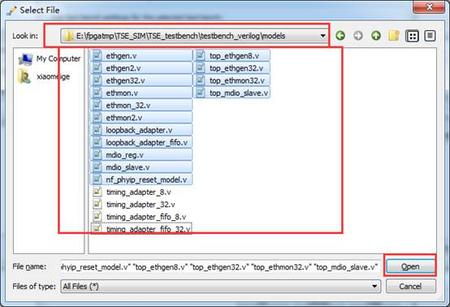

进入文件选择选项卡中,将目录定位到工程目录下的

” <IP名>_testbench/testbench_verilog/models”文件夹中,选择除以timing开头的文件(时序仿真时才需要用到)以外的其他所有文件,点击Open。如下图所示:

这些文件都是为了配合仿真TSE IP核而存在的,属于仿真模型,这些文件组合在一起相当于虚拟了一个物理的网络收发器PHY。这样,就能够模拟真实的板级环境进行仿真测试了。

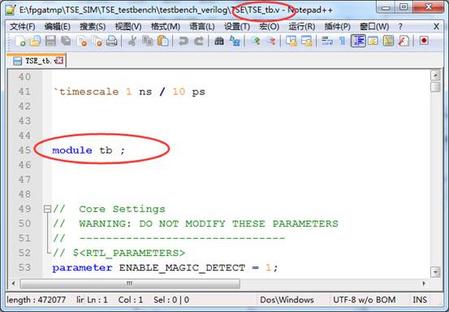

在New Test Bench Settings选项卡中,Test bench一栏中输入<IP名>_tb,Top Level module in test bench一栏中输入tb。至于这里为什么要手动输入tb,而不是由软件自动填充的<IP名>_tb。

为什么是这样,这里小梅哥最开始也郁闷了很久,我最开始也是直接使用<IP名>_tb来填入top Level module in test bench中,结果modelsim – altera中仿真总是报错,提示找不到<IP名>_tb.V文件,我就郁闷了,明明是已经加入进来了,为什么进行仿真时总说找不到呢?直到后来我打开<IP名>_tb.V这个文件一看,才找到了原因,如下图所示:

虽然文件名字是<IP名>_tb.V,但是文件中test bench的顶层实体名字任然是tb,因此,我们直接设置<IP名>_tb.V作为top Level module in test bench的名字当然不对了,所以我们需要根据实际情况,输入top Level module in test bench的名字为tb。

设置完毕,连续点击两次OK,回到Settings - <工程名>选项卡中,勾选Use Script to setup simulation,并定位到文件<IP名>_testbench/testbench_verilog/<IP名>/<IP名>_wave.do。这个文件是一个脚本文件,主要功能是有条理的添加信号到仿真波形窗口中,以使我们看起来更加直观,如下图所示。

然后apply,OK即可。此时在Quartus II软件中点击RTL Simulation按钮即可启动仿真,如下图所示:

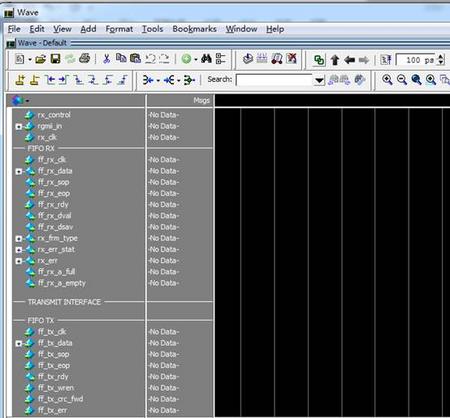

整个过程较为漫长,modelsim-altera需要首先对设计文件进行编译,然后才能运行仿真,大约需要3分钟左右的时间吧。仿真开始后,会自动在波形窗口中添加好信号并停在仿真时间0处,如下图所示:

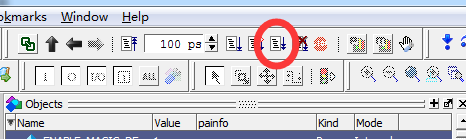

因为仿真脚本中没有run这个命令,所以添加完波形后modelsim就进入等待状态,因此我们必须手动输入run –all命令,或者在GUI上点击run –all按钮来运行仿真,如下图所示:

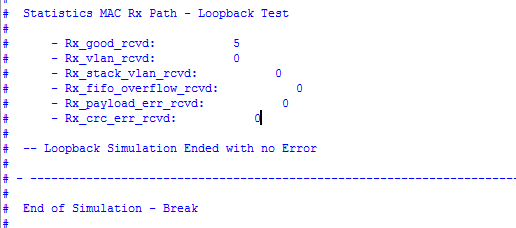

仿真大约运行10秒左右就会停下来,此时就可以观察波形了,在Transcript窗口中也会打印仿真过程中的一些数据信息。下图为仿真结果欣赏:

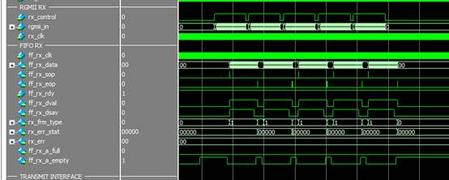

接收模块和接收FIFO模块信号仿真波形:

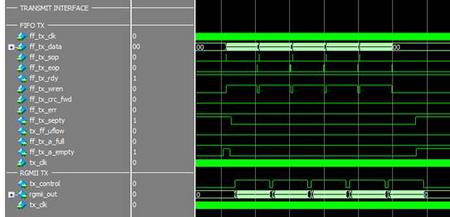

发送模块和发送fifo模块仿真波形:

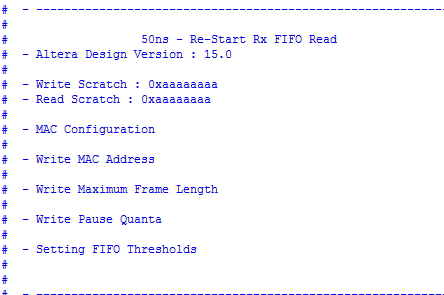

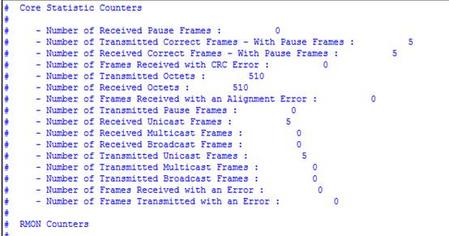

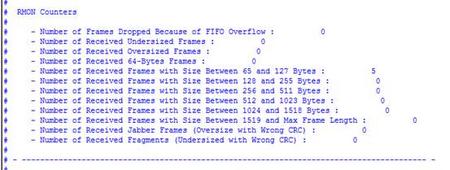

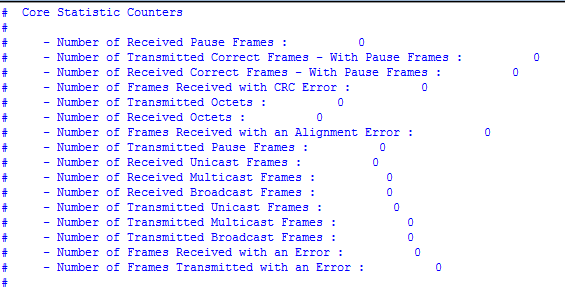

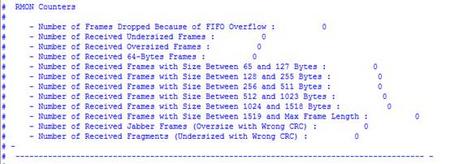

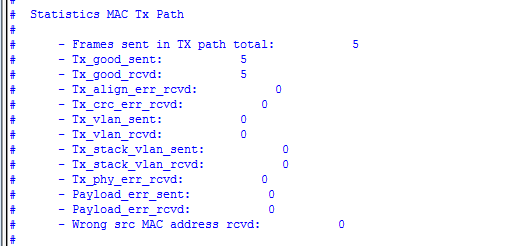

打印的信息:

今天只是做了IP核的功能仿真,暂时还没有对仿真结果进行分析,这个留到后面具体做通信数据的时候再来做。小梅哥年轻,经验不足,博客中若有什么不妥之处,欢迎各位指正。

小梅哥

2015年6月19日于北京至芯科技

/5

/5

文章评论(0条评论)

登录后参与讨论