小梅哥FPGA学习笔记之Quartus II 15.0中仿真DDR2 IP核

虽然近期用不上DDR2的控制器,但是昨天成功仿真Altera 三速以太网IP核又确实让我兴奋了一把,趁着这个兴奋劲儿,再一举拿下DDR2的IP核仿真。

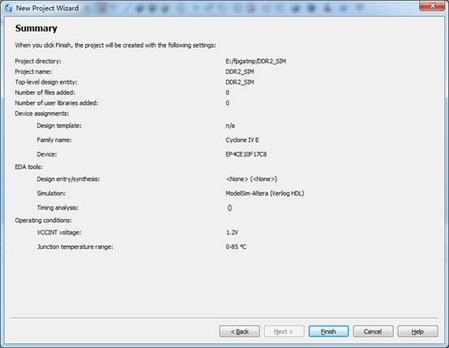

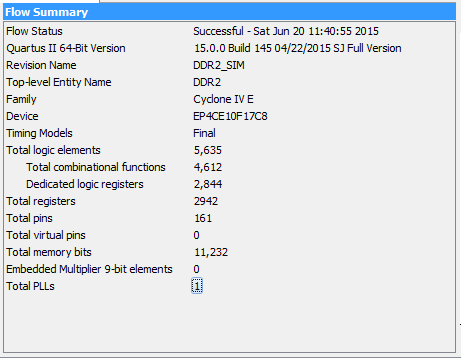

仿真还是在Altera 最新的开发套件Quartus II 15.0中进行。首先创建工程,我将工程命名为DDR2_SIM,器件选择我比较熟悉的EP4CE10F17C8,仿真工具选择modelsim – altera ,语言为Verilog。最后,整个工程建立完毕后的Summary如下图所示:

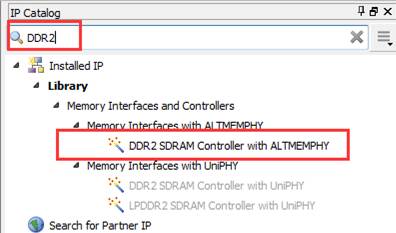

工程创建好后,在右侧的IPCatlog中,搜索栏处输入DDR2,然后在搜索结果中选择DDR2 SDRAM Controller with ALTMEMPHY,如下图所示:

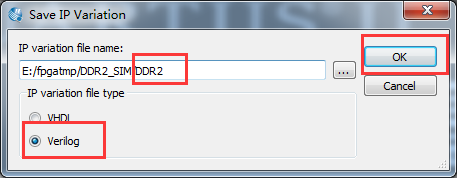

双击DDR2 SDRAM Controller with ALTMEMPHY,会弹出如下所示的对话框:

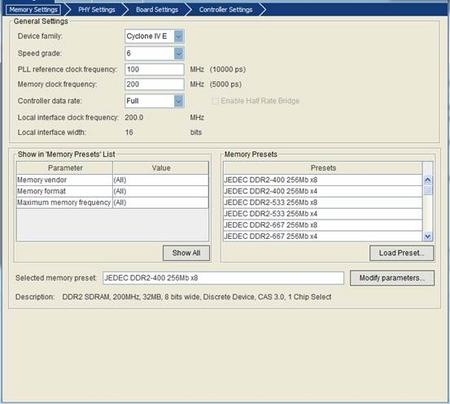

将该IP命名为DDR2,语言选择Verilog,然后点击OK,就会开始加载参数设置对话框,整个加载过程大约需要等待20到30秒左右才会弹出GUI界面,请大家耐心等待。弹出的GUI 界面如下所示:

很遗憾,整个界面还是显示不全,上半部分无法看到,也无法拖动窗口,原本右下侧的finish和cancel按钮也没有显露出来,这个问题我从使用Quartus II11.0的时候就发现了(没有用过10.x版本,据说是从10.x版本开始出现这个问题的),到了Quartus II 15.0中这个问题依然没有得到解决,还是希望Altera能够尽快修复这个Bug。

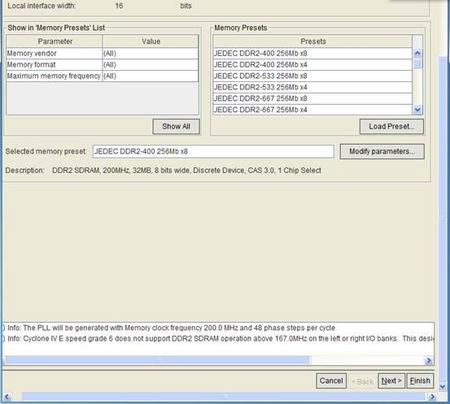

虽然界面默认没有完全显示,但是我们还是有办法来让他显示的。如果你不需要移动这个配置窗口的位置,或者说对界面最上方未显示的部分内容已知或者不关心(实际我们也真的不用去关心)那么简单的解决方法就是单击系统右下角的显示桌面按钮(win7),然后再在任务栏中点击该配置界面,就能够成功加载右下角的finish和cancel按钮了,但是界面上半部分依旧无法看到。如下图所示:

但是此时依旧无法看到上半部分,终极解决方案就是,

第一步:打开这个配置界面的GUI

第二步:设置电脑屏幕分辨率为最小值(我是这么做的,不清楚设置其他分辨率是否也能奏效)

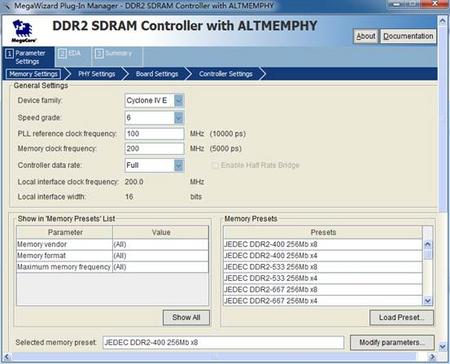

第三步:将屏幕分辨率修改回正常值。这时候再看,整个界面就能够正常显示了,如下图:

拖着右侧的进度条往下划就能看到finish和cancel按钮了。同时页面最上方的内容也能看到了。

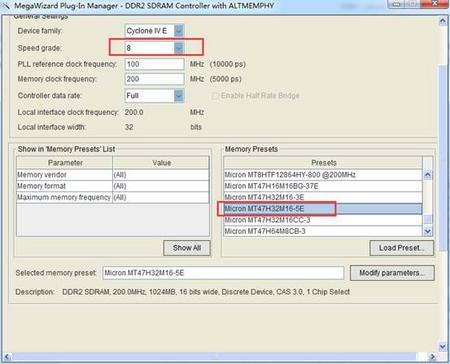

这里我们在Memory选项卡中,设置速度等级(Speed Grade)为8,与实际芯片保持一致。Memory Presets为“Micron MT47H32M16-5E “,如下图所示:

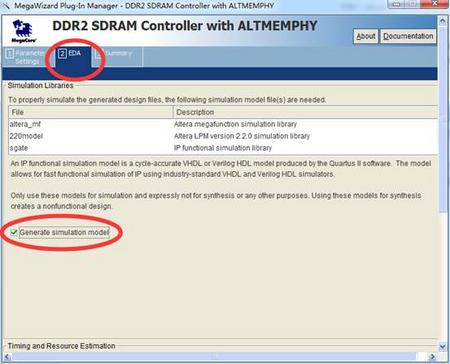

此页中其他选项保持默认,接下来的若干项均保持默认即可,直到切换到EDA选项卡处,勾选Generate Simulation model,这里是为了仿真时生成仿真模型,以配合modelsim进行仿真。

点击右下角的finish,软件则开始生成IP核控制器的相关文件和示例内容。生成完毕大约2分钟。

生成完毕后,设置DDR2.qip为设计顶层模块,然后执行分析和综合(快捷键是Ctrl + K)。

分析和综合完成后,整个IP核占用资源如下图所示:

话说这个控制器还是挺耗费资源的啊。

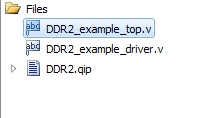

接下来设置仿真,有了昨天仿真TSE时遇到testbench文件名与文件中实体名不一致的经历,这次我又首先去查看了下testbench,这次还好,testbench文件名和文件中的实体名是一致的。不过一个疑问就是,为什么testbench的名字是叫做DDR2_example_top_tb.v而不是DDR2_ tb.v?仔细一查看这个文件才发现testbench文件中例化的设计名字居然是DDR2_example_top而不是我想当然的DDR2。也就是说,这个设计是将控制器和例子独立开来了,这一点和昨天仿真的TSE不同,TSE的仿真文件中直接以IP核为设计顶层,而DDR2中确是另外做了一个DDR2_example_top文件来作为例子的顶层。查看DDR2_example_top文件,其中例化了DDR2控制器和一个DDR2_example_driver文件。于是我回到Quartus II中,手动添加DDR2_example_top.V和DDR2_example_driver.V文件到工程中来,并更改DDR2_example_top.V为设计顶层文件,然后分析和综合。

接下来设置NativeLink以将设计工程和Modelsim-altera关联起来。

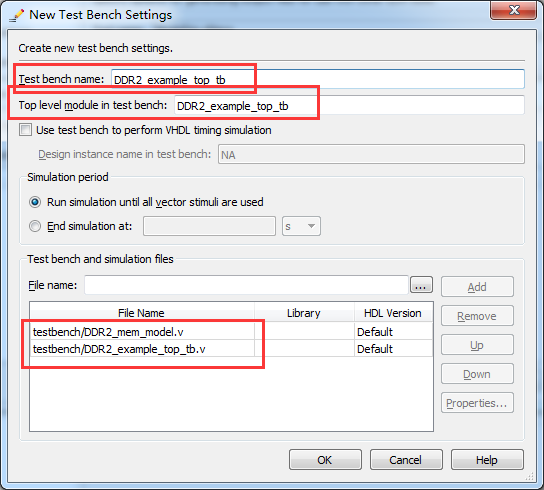

设置testbench为这里具体怎么添加文件我就不多说了,详细请参考我仿真三速以太网时的介绍。

需要添加的testbench文件有两个,位于testbench文件夹下,分别为DDR2_example_top_tb.v和DDR2_mem_model.V。其中DDR2_mem_model.V是一个DDR2的仿真模型,该模型直接用行为语言描述了一个虚拟的DDR2器件,这样,通过DDR2控制器来操作这个虚拟的器件,就能够保证控制器得到正常的操作相应,从而使仿真正常的进行下去。

添加完成后,设置Test bench name和top level module in test bench 为DDR2_example_top_tb。然后一路点击OK下去,直到设置完毕。 如下图所示:

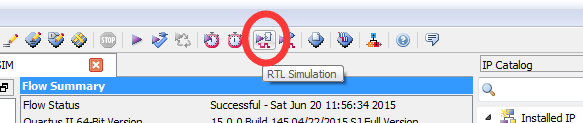

接下来,就可以直接点击RTL Simulation按钮执行仿真了:

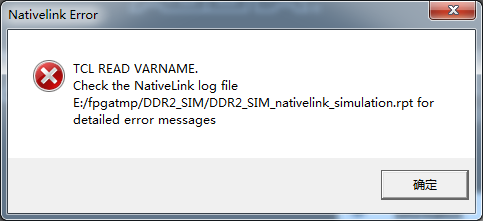

一切,本以为一气呵成,没想到在运行仿真的时候具体弹出下面这个错误,我改了好久都搞不定,不知道是我操作有问题还是软件Bug,或者Quartus II15.0与我使用的modelsim不兼容(我使用的是Quartus II13.0配套的modelsim – altera来仿真的,有可能是兼容性问题,但是我后来换成modelsim se 10.4d也还是不行),总之很郁闷,我使用的是骏龙科技FAE赠送的60天全功能License,因此应该也不是License的问题。再查看rpt文件,也没有找到任何的线索。

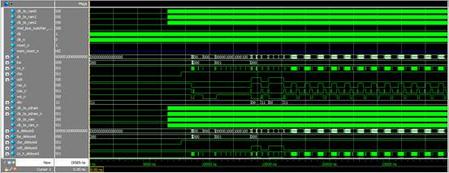

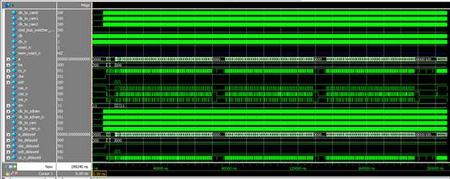

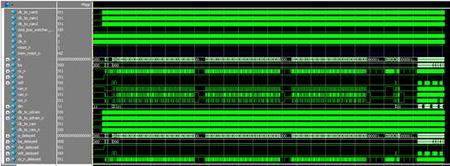

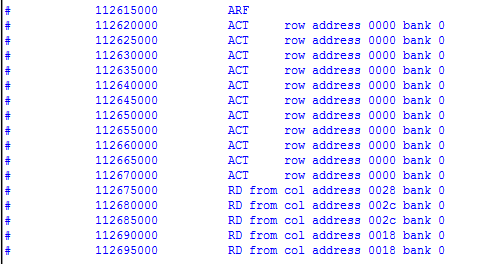

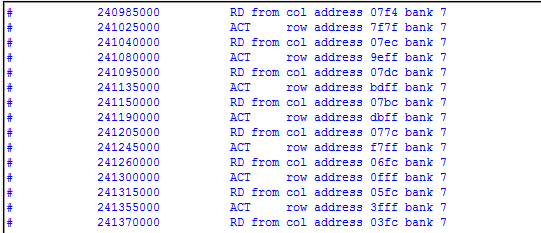

无奈之下,只得回到Quartus II 13.0的软件中,重复整个过程,结果顺利完成(Quartus II 13.0中添加DDR2 IP核是在MegaWizard Plug-In Manager中这一点与Quartus II 15.0中不同,其他均完全一致)。仿真结果如下图所示(具体分析波形的结果本文就不介绍了,留到后面哪一天需要用到DDR2的时候在来弄,精力有限啊):

另外,谁要是使用Quartus II15.0能够仿真成功,或者解决了我遇到的问题,也希望阁下不吝赐教。

小梅哥

2015年6月20日于北京至芯科技

用户1822651 2016-6-3 11:46

用户377235 2015-12-7 15:30

用户377235 2015-11-2 14:41

用户436812 2015-9-2 16:54

用户1845900 2015-7-21 14:21

用户431679 2015-6-30 11:27

用户377235 2015-6-29 10:30

用户602479 2015-6-25 09:13