小梅哥FPGA时序分析从遥望到领悟系列

没有遇见过I/O时序问题,没有通过I/O约束方式实际解决过I/O时序问题,就很难明白I/O约束的重要性,也很难相信各种EDA软件真的有那么的傻白甜。

我遇到的最典型的一个I/O不加约束导致设计异常,然后通过加入合理的I/O时序约束解决问题的例子,就是第一节里面提到的基于ADV7123芯片的RGB数字时序转VGA模拟时序的例子。

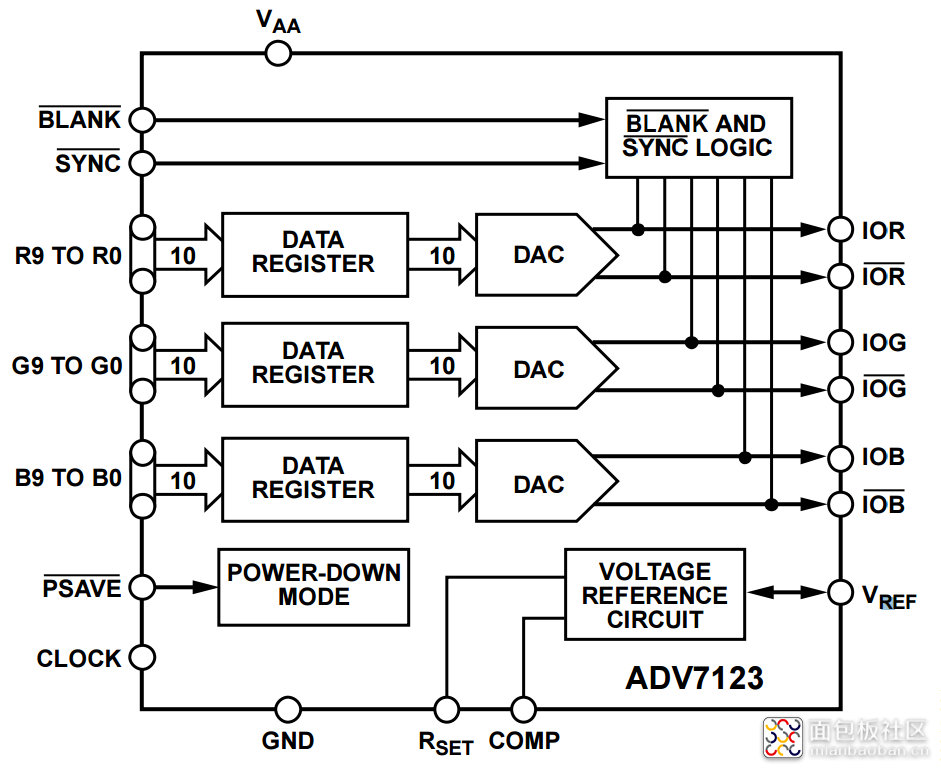

ADV7123这个芯片,相信大凡接触过基于FPGA的VGA显示的网友都了解,无论是国际大厂友晶的DE1、DE2开发板,还是我们(小梅哥FPGA)的24位高动态VGA输出模块,都是使用的该芯片实现的,这个芯片实际上就是一个集成3路10bit并行DAC的DAC芯片。其系统架构如下图所示:

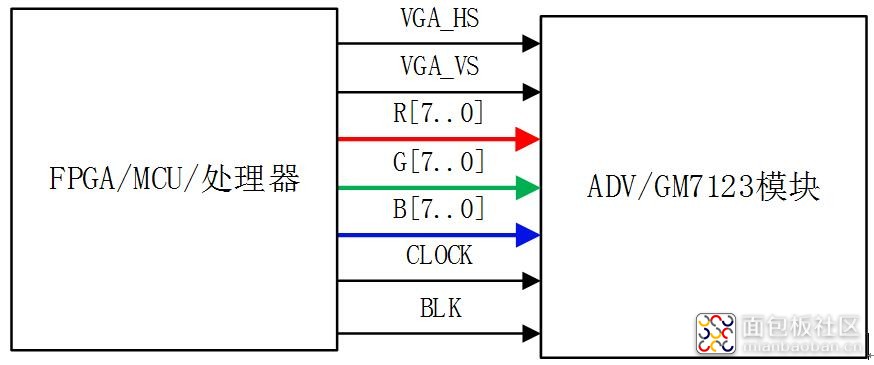

通过结构图可以看到,该芯片的结构确实简单,总共3个10位的DAC芯片,分别对应RGB彩色数据的RED、GREEN、BLUE三元色,同时,每个元色的数据接入芯片后,会首先在数据寄存器上寄存一拍,然后再送给各自的DAC转换为模拟信号输出。其中,在数据寄存器上进行同步时,使用的是FPGA输出给ADV7123的CLOCK信号,下图为FPGA或处理器使用RGB888模式连接ADV7123芯片示意图。

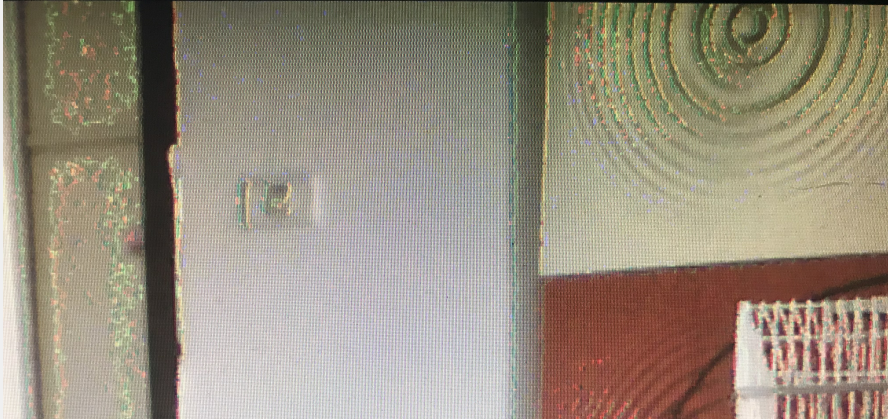

好了,电路讲完了(貌似啥都没讲),接下来该说正事了。先让我们看看,不加任何处理直接将FPGA内部的时钟作为CLOCK提供给ADV7123芯片作为数据同步时钟的具体现象,以OV5640型CMOS摄像头采集1280*720分辨率的图像,经由ADV7123芯片送给VGA显示器为例。

以下为了原汁原味的展现图片的效果,不想因为网络压缩导致图片失真,所以图片统一用BMP格式了,对不住了,各位网友的流量,更对不住了,面包板社区的服务器。 ,如果您网速不行的,可能要等一会儿才能打得开图片。

,如果您网速不行的,可能要等一会儿才能打得开图片。

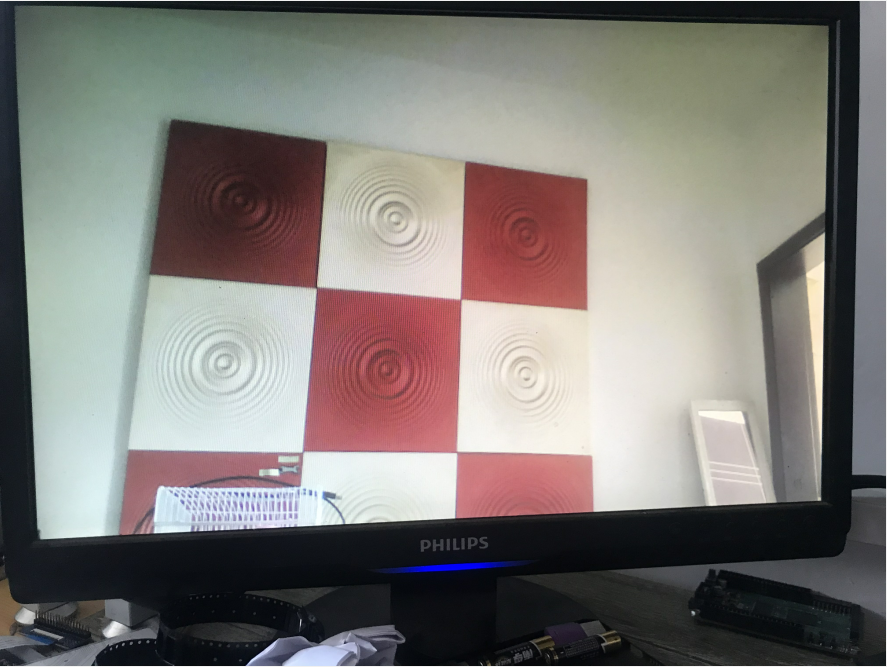

上图为不加任何I/O约束,也不对FPGA输给ADV7123芯片的CLOCK时钟进行取反的情况下采集到的图像实拍(时钟约束这种基本的条件当然已经满足了),可以看到,在轮廓的边缘,有明显的杂色出现,例如电视墙右上角那个红色块的中间圆圈处,能够看到明显的杂色。如果上图看的还不是很清楚的话,那么下面图片为该照片中局部放大图,通过局部放大图,看到的现象更加明显。

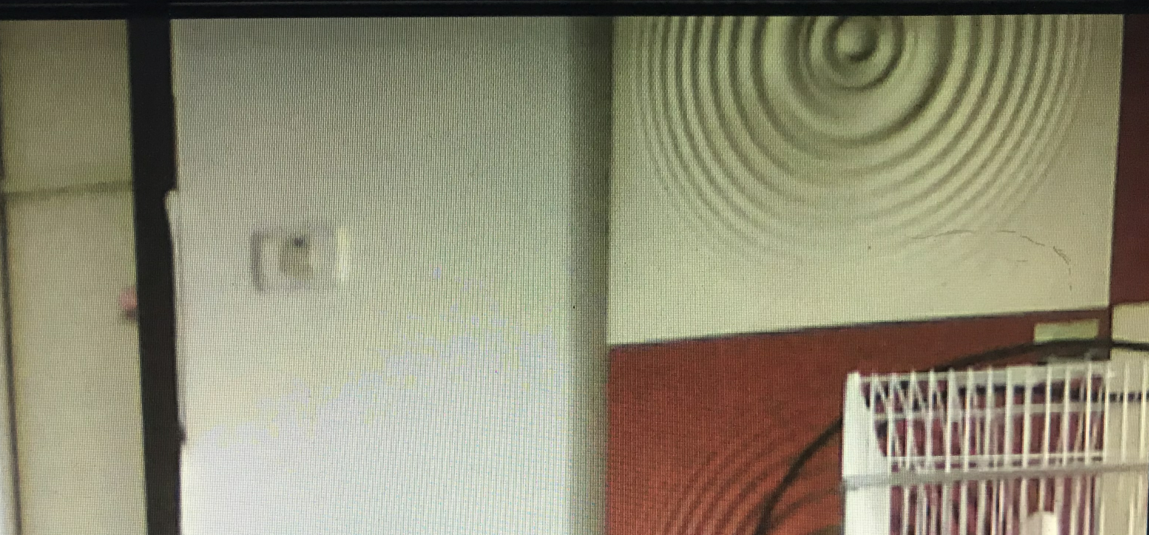

从上图可以明显看到,在两个方块的边缘处,就像是发了霉一样的附着着很多杂色,如果还觉得不明显的话,换个角度,拍个更加明显的效果图,如下所示:

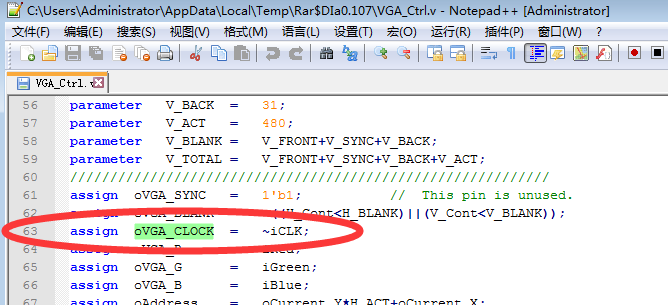

好了,问题确实是实际存在的,毋庸置疑,哪怕是同样的实验,放在友晶的DE2-115这种原厂开发板上也是同样的现象。那么这个问题该怎么去解决呢?在DE2-115开发板提供的一个名为“DE2_115_TV”的Demo里面,可以看到,友晶也是将VGA控制器逻辑代码的工作时钟iCLK取反后输出的,如下图所示。所以,也正是这样,网上能够找到的绝大部分基于ADV7123芯片的代码也都是使用的这种方法(那种基于电阻网络的Low成本VGA方案本身性能就很差,根本没有同步时钟信号,因此没有这个说法)。

那么这种将时钟取反的方法是否真的有效呢?答案是肯定的!该方案不仅有效,而且还良好的工作在各种开发板上,不论是友晶和Altera等原厂开发板,还是其他厂家出的一些实验箱或者学习板,无论是芯片直接通过高可靠性的PCB板直接和FPGA芯片连接,还是用2.54mm的排针接口经过各种转接插接,该方案都能近乎完美的解决问题。比如,在我们的代码中,按照这个思路,将该时钟信号取反后作为送给ADV7123芯片的CLOCK信号输出,VGA显示器上显示的图像效果立马变正常了,如下图所示。

同样的,作为一个清晰的对比,下图为将上图中的局部区域放大,可以看到,细节位置依旧白白净净,没有发霉的样子。

换个角度,拍个更加明显的效果图,效果依旧也是美美哒,如下所示:

此刻,是不是有人差点笑出声来:噗嗤,原来就这样啊,那你扯那么复杂,又臭又长的,好了好了,别说了,我知道了。

如果单就解决这个问题来说,确实是按照上面的方法弄一下,又快又有效,而且放之四海而皆准。可是,从学习的角度来说,是不是达到这样的效果,我们就应该满足了呢?在这一个取反符号引发的惊天逆转的背后,究竟隐藏了多少不为人知的秘密,是代码设计的缺陷,还是硬件板卡的低劣,亦或是还有什么原因,是我们目前还不知道的呢?预知后事如何,且听下回分解。(捂头疯狂逃窜,因为我有一种被打的预感。)

作者: 小梅哥., 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-452191.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/1

/1

curton 2019-9-3 21:08