小梅哥FPGA时序分析从遥望到领悟系列

以前,那是在以前,经常有网友(原谅我行文动不动就是网友说,网友问,毕竟我是卖开发板的,正面接触学FPGA的网友相对多一些,所以这些也都是事实存在的事情)问我:小梅哥,请问在什么情况下需要进行时序约束呢?我的系统跑50M,请问不加约束行不行?我的系统跑100M,一定需要加约束吗?怎么加呢?面对这样的提问,我一般都是比较官方的回答:一般你们学习中进行的简单的系统设计,比如跑跑VGA、UART、SPI等简单的系统,加不加都行,100M的情况,简单的系统也可以不用加,复杂的加个时钟约束就可以。然后,基本上对话到这里就结束了,我也就松了一口气,因为他们没有问为什么,如果问为什么,或者问怎么加,那就得费很多的力气去说明,当然人家还不一定马上就能理解。也是怕自己说的不准确,让人更加迷糊。这样的回答,一直到2017年暑期FPGA辅导的时候,有学员在学习SOPC课程的时,发现同样的工程,即使Quartus工程和Qsys中系统不做任何修改,重新编译一次Quartus工程得到的sof文件下载到开发板中,在Eclipse中执行Run操作(使用Jtag下载elf文件到FPGA中)时,有时候能正常下载并运行,但是有的时候下载都下载不成功,即使是我对该学员的工程进行了细致的分析,从Qsys中每个IP的每个信号的连线,到Quartus中工程文件,以及引脚分配,还有Eclipse中各种设置都进行了详细的检查,甚至更换了开发板进行测试,都是这种现象。在和众多学员进行了多番分析,挠破了几层头皮(请忽略漫天飞舞的雪花)之后,我突然灵光一闪,会不会是因为系统跑不到100MHz呢,换句话说,是不是这个系统在当前的布局布线的情况下,其fmax远低于实际工作的时钟频率100MHz呢?带着这样的疑问,我们马上对该学员的系统进行了时序分析。

首先可以确定,该学员并没有对该工程添加基本的时钟约束,查看时序报告,也没有报告有任何软件默认的时钟约束。所以,我们立即对该工程加入时钟约束。

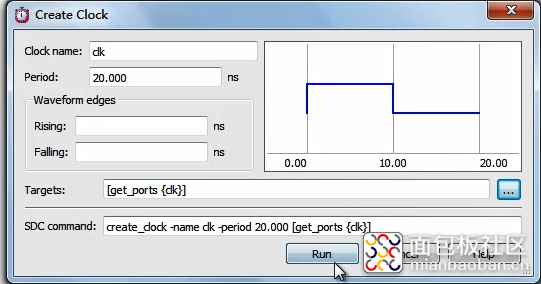

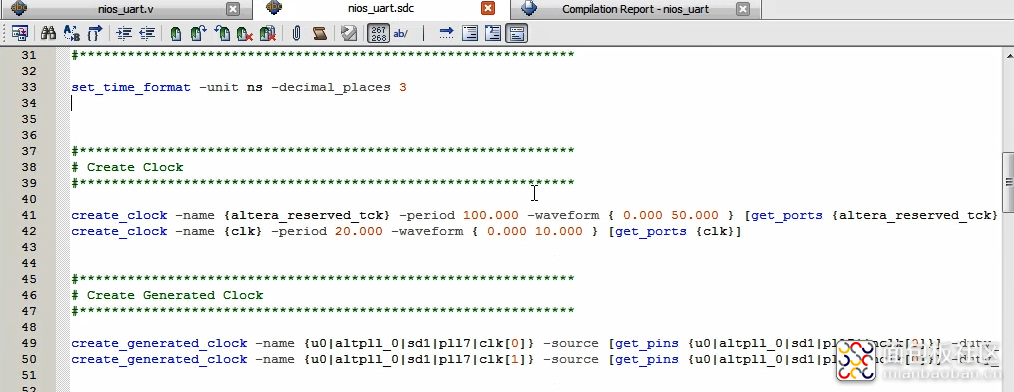

第一步,加入时钟约束,操作很简单,就是下述界面了

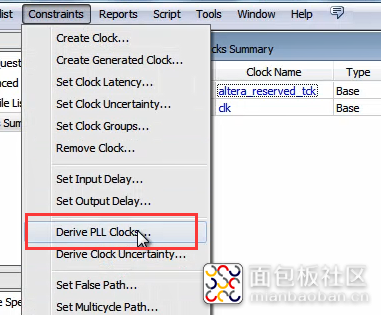

第二步,派生PLL时钟。因为在该工程中,是将输入自外部50MHz晶振时钟信号作为FPGA片上PLL的参考时钟,经过倍频得到100MHz的时钟信号,该100MHz的信号再作为整个设计的时钟信号使用。所以,需要加入PLL的时钟约束。操作很简单,就是下述界面了,只需要执行derive_pll_clocks命令就可以了,如下图所示。

第三步,报告时钟约束。通过报告时钟约束命令,可以查看当前系统的所有时钟约束。可以看到,经过以上两步操作后,再执行报告时钟约束命令,发现系统中就有了clk和pll|clk[0]和pll|clk[1],

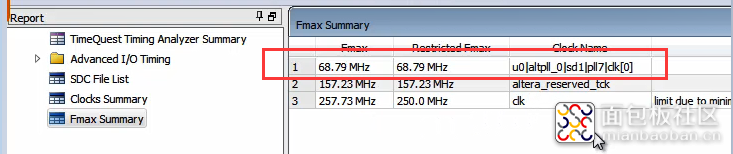

第四步,查看运行最大频率。通过报告最大频率命令,可以查看当前经过布局布线的网表能够运行的最大时钟频率,如下图1。可以看到,在本例中,作为最重要的所有寄存器的工作时钟的pll7|clk[0]时钟,其最大运行频率竟然只有惊人的68.76MHz。这个工程还只是简单的在Qsys中加入了一个NIOS II CPU、一个SDRAM控制器、一个LCD1602模块呀,这么简单的一个系统,在不加时钟约束的情况下,居然只能最高运行到68.79MHz,可想而知,如果系统中再加入更多的外设,比如加入一些PIO、SPI、FIFO、UART等之后,系统的最高运行频率可能会进一步下降,更进一步,如果加入了那些本身都很复杂的IP,比如DMA、视频处理IP之后,整个系统的最高运行频率可能会低于50MHz。

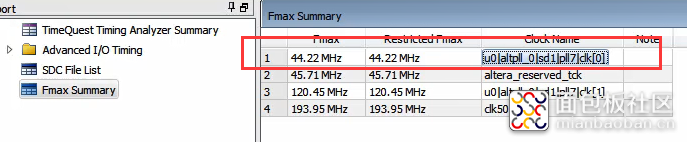

上面说加入更多的IP之后,如果不加时钟约束,整个系统的最高运行频率可能会低于50MHz的事情绝对不是危言耸听,而是有众多网友见证的公开课现场演示分析的过程,详细可以参看小梅哥2017年时候录制的公开课“基于SOPC的2.8寸液晶显示屏应用”一课的第1小时36分到1小时54分的内容,该课程可以在我们的官网 网站上找到,下图为该视频中进行分析得到的报告,可以看到,时钟频率仅为44.22MHz。

看到这里,不知道大家是什么感受,反正我当时看到这个结果的时候是后背发凉。因为如果是这样的话,那么我之前回答网友的,系统频率跑50MHz的时候可以不加时序约束的说法就是不合适的。因为如果不注重代码设计,或者系统设计较为庞大,在不加约束的情况下,整个系统的运行频率可能真的连50MHz都不一定能达到。

第五步,使用约束文件指导Quartus工程进行编译。通过上面的例子,我们可以发现,在不加约束的情况下,Quartus对设计的布局布线会比较随意,得到的编译结果的最高运行频率可能会比较低。然后我们将上述约束内容生成约束文件(sdc),并添加到Quartus工程中(如下图)之后,再次进行全编译。

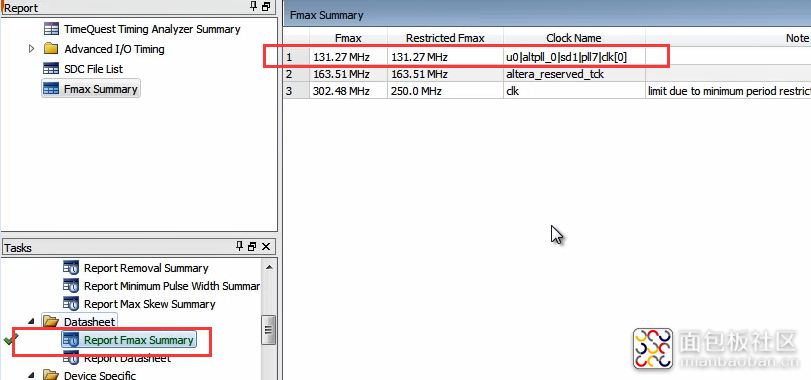

第六步,查看加入约束后的编译时序报告,编译完成之后查看时序报告,发现整个系统的最高运行频率竟然能够达到131.27MHz,如下图所示。

至此,石锤了如果不加入最基本的时钟约束,Quartus软件可能真的不会按照最优秀的布局布线规划给我们进行编译的问题,同时也打脸了我之前给网友的不严谨的回答。所以此时,我必须要重新组织我对之前网友提问的答案了:无论什么样的系统,都建议加入完整的时序约束,以保证Quartus软件去按照我们明确的时序约束对设计进行必要的优化。即使是一个非常简单的系统,加入基本的约束也是有意义的,因为这能让我们养成无约束,不设计的良好习惯。

冷汗过后,相信大家也应该明白我在第一节里面说的,越来越不敢写教程的原因了。不过,不敢写教程,不等于不愿意分享,如果我自己写的笔记和分析之类的文章能够得到大家的认可,相信不用我自己喊口号,大家也愿意将其当成教程来学习,来推荐。

到此为止,可能大多数人以为时序约束就差不多了。曾经我也是这样认为的,因为在之前的网络上,能找到的资料大部分也都是详细介绍到这里就差不多了,其他的一些约束内容,大多一笔带过,让人误以为那些并不重要,实际上,从一个完整的PCB板级系统可靠性来讲,那些他们没有详细讲到的地方更加的重要,还记得我在第一节说过的USB的问题、VGA的问题吧,那些问题,单靠通过加入简单的时钟约束是无法解决问题的。因为时钟约束只能约束FPGA芯片内的各个路径,而对FPGA和其他芯片的连接,也就是IO口上的时序约束根本无能为力,所以,要想解决这些问题,就涉及到另一个更加重要的约束了——IO约束。什么是IO约束,IO约束真的能解决这些问题?预知后事如何,且听下回分解。

作者: 小梅哥., 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-452191.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

curton 2019-9-3 21:08

用户3893407 2019-7-1 15:13

用户284745 2019-6-30 15:53

用户3893396 2019-6-30 14:35

用户3893396 2019-6-30 14:35

用户3893210 2019-6-23 20:47

用户1013590 2019-6-22 18:46