程序

module mux4_1(a,b,c,d,s,out);

input a,b,c,d;

input [1:0] s;

output out;

reg out;

always@(a,b,c,d,s)

begin

case(s)

2'b00:out = a;

2'b01:out = b;

2'b10:out = c;

2'b11:out = d;

default:out = 0;

endcase

end

endmodule

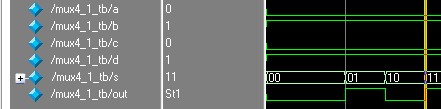

测试程序

`timescale 1ns/1ns

module mux4_1_tb();

reg a,b,c,d;

reg [1:0] s;

wire out;

mux4_1 mux(a,b,c,d,s,out);

initial

begin

s = 2'b00;

a = 0;

b = 1;

c = 0;

d = 1;

#10

s = 2'b00;

#10

s = 2'b01;

#10

s = 2'b10;

#10

s = 2'b11;

end

endmodule

/2

/2

文章评论(0条评论)

登录后参与讨论