SOPC快速入门

1.实验设备

硬件:SmartSOPC教学实验开发平台

软件:Quartus II10.0,SOPC Builder10.0,Nios II IDE10.0

2.实验步骤

1)使用Quartus II建立工程

(1)启动Quartus II软件并建立工程

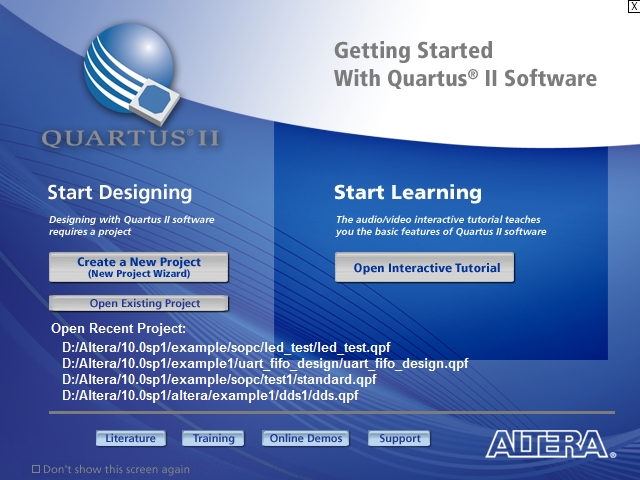

启动Quartus II10.0软件,软件界面如下:

新建工程,点击

指定工程目录、名称和顶层实体。本例工程的路径为D:/Altera/10.0sp1/example1/led_test,工程名与顶层文件的实体名同名为1.jpg">

单击 ,指定工程设计文件,进入如图对话框:

,指定工程设计文件,进入如图对话框:

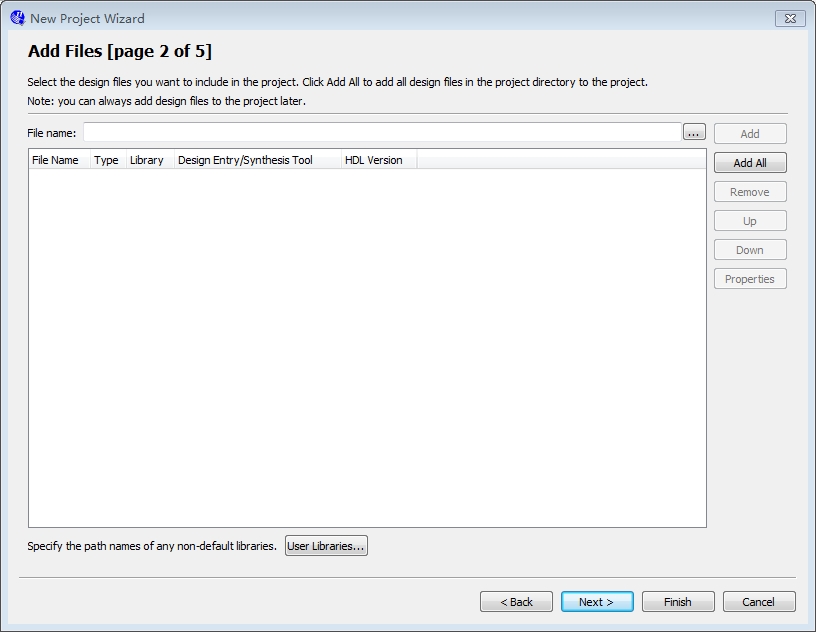

由于是新建工程,暂无输入文件,直接单击 ,指定该设计的Altera器件系列,这里我们选择QuickSOPC核心板上所用的Cyclone系列的EP1C6Q240C8,如下图所示:

,指定该设计的Altera器件系列,这里我们选择QuickSOPC核心板上所用的Cyclone系列的EP1C6Q240C8,如下图所示:

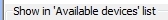

在上图的 ,设计者可以通过指定封装、引脚数以及器件速度等级来加快器件查找的速度,如下图所示

,设计者可以通过指定封装、引脚数以及器件速度等级来加快器件查找的速度,如下图所示

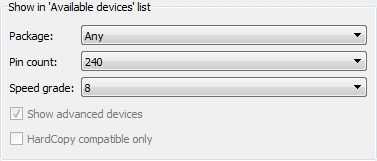

指定器件完成后,单击 ,指定用于该工程的其他EDA工具,如下图所示:

,指定用于该工程的其他EDA工具,如下图所示:

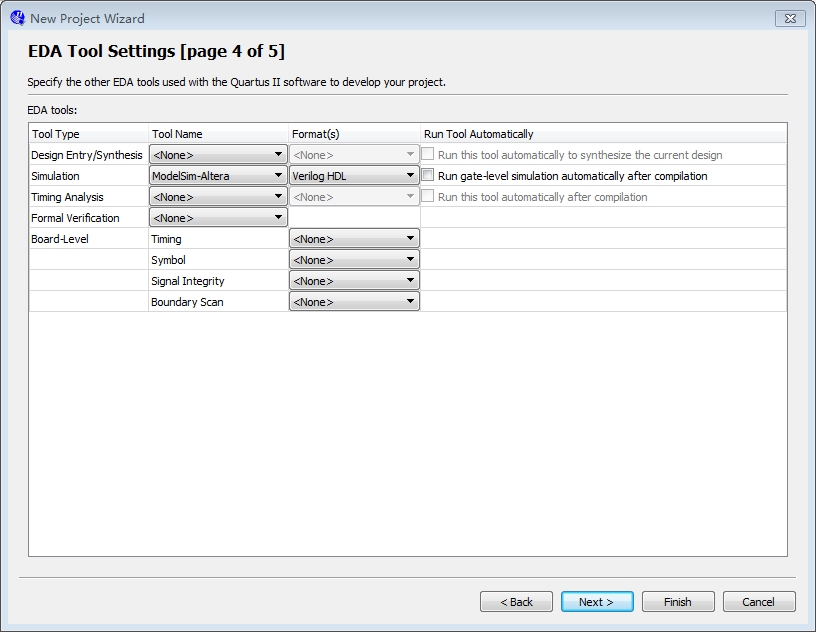

单击 ,设计者可以看到工程文件的配置信息报告。单击

,设计者可以看到工程文件的配置信息报告。单击 ,完成新建工程的建立。如下图:

,完成新建工程的建立。如下图:

(2)建立顶层模块

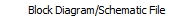

选择File--New打开新建文件对话框,选择 ,如下图:

,如下图:

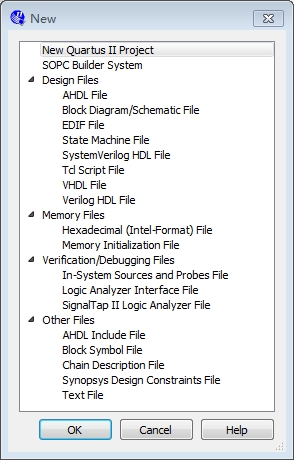

单击 建立一个空的顶层模块,缺省名为Block1.bdf。选择File--Save As打开如图对话框,如下图:

建立一个空的顶层模块,缺省名为Block1.bdf。选择File--Save As打开如图对话框,如下图:

至此,顶层模块的建立完成。下面的步骤主要将SOPC Builder生成的模块加入到顶层模块中。

2)使用SOPC Builder创建Nios II系统

(1)启动SOPC Builder

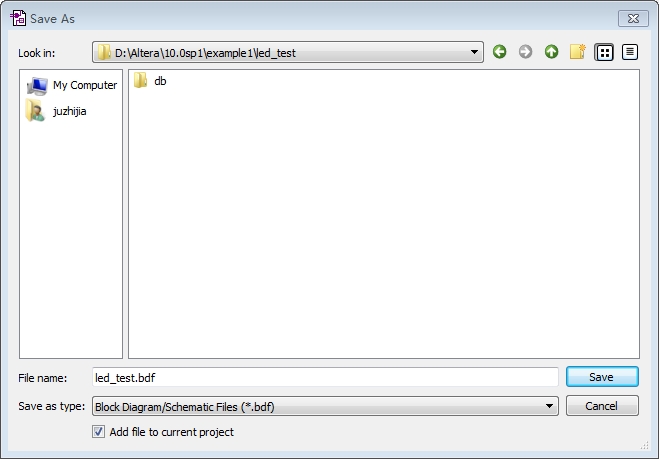

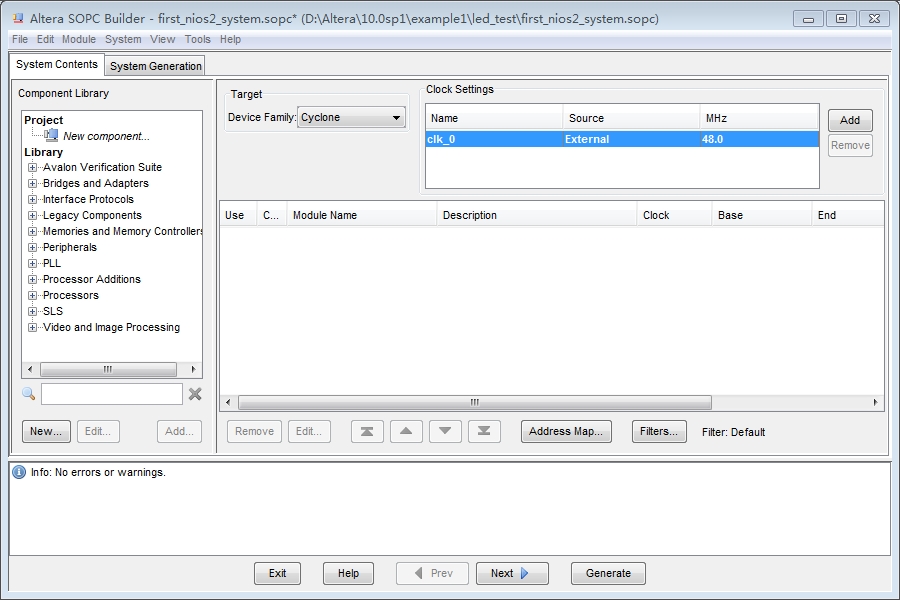

点击图标 ,启动SOPC Builder,启动后的对话框如下图所示:

,启动SOPC Builder,启动后的对话框如下图所示:

在上图中输入系统名称并选择目标硬件语言。系统名为first_nios2_system,目标硬件语言为Verilog。

单击 按钮,进入SOPC Builder图形界面。

按钮,进入SOPC Builder图形界面。

(2)指定目标FPGA和时钟设置

定制系统前,需要指定系统的时钟频率。SOPC Builder将利用这个时钟频率来产生时钟分频或波特率等。注意,所设置的频率要与系统实际运行的时钟频率相匹配。本实验选择的是48MHz,如下图:

(3)添加Nios II处理器内核

添加Nios II/s内核到系统的步骤如下:

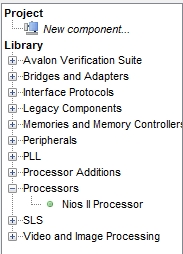

在Library目录下的Processors目录下双击Nios II Processing,如下图:

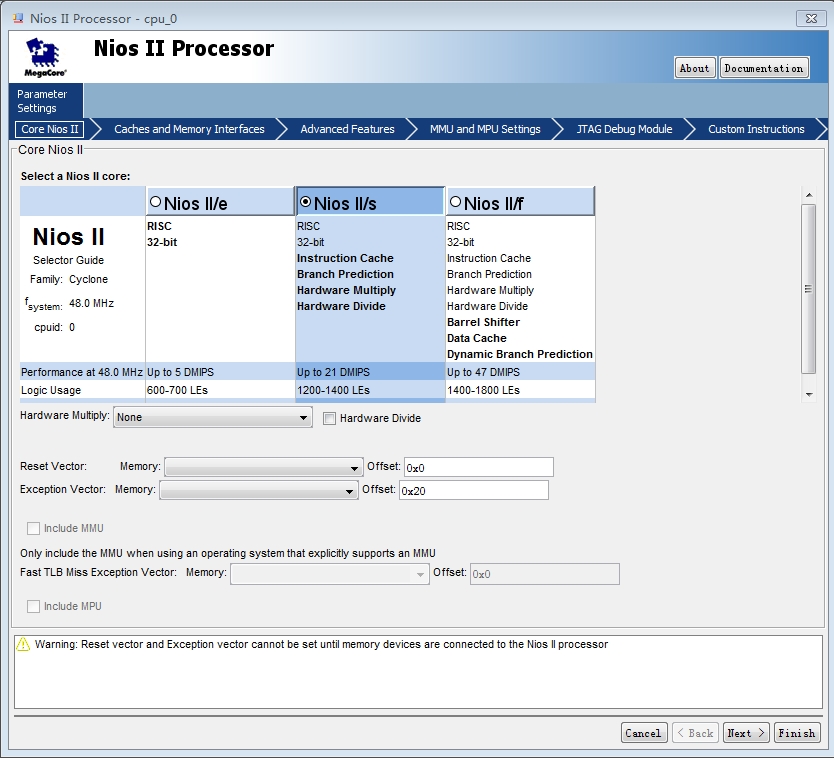

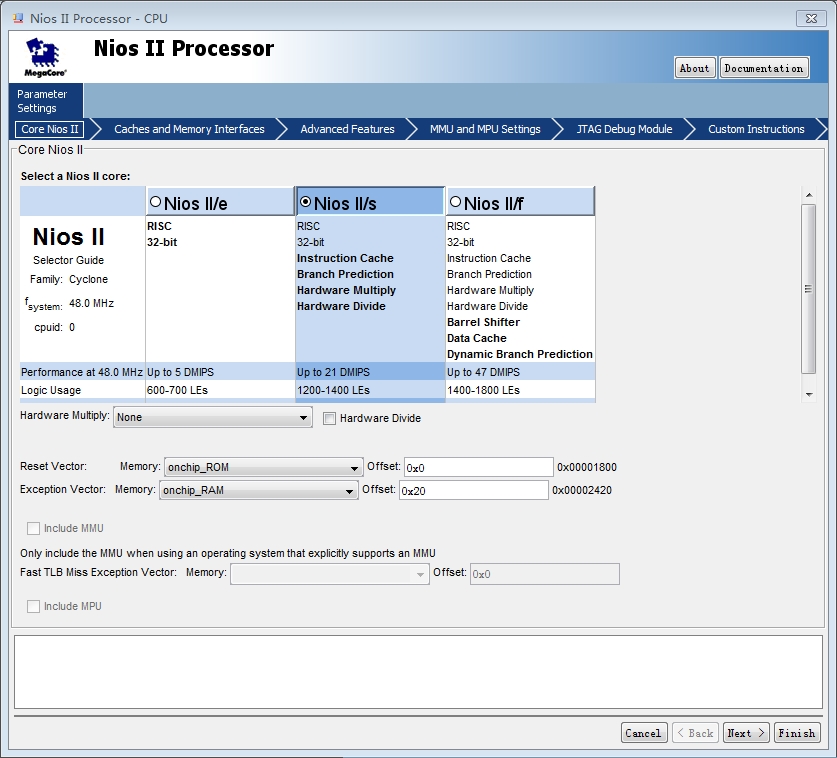

出现下图所示的Altera Nios II配置向导:

指定下列设置:Nios II Core:Nios II/s Hardware Multiply:None Hardware Divide:不选中

: 硬件乘法器

: 硬件乘法器  :硬件除法器

:硬件除法器

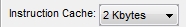

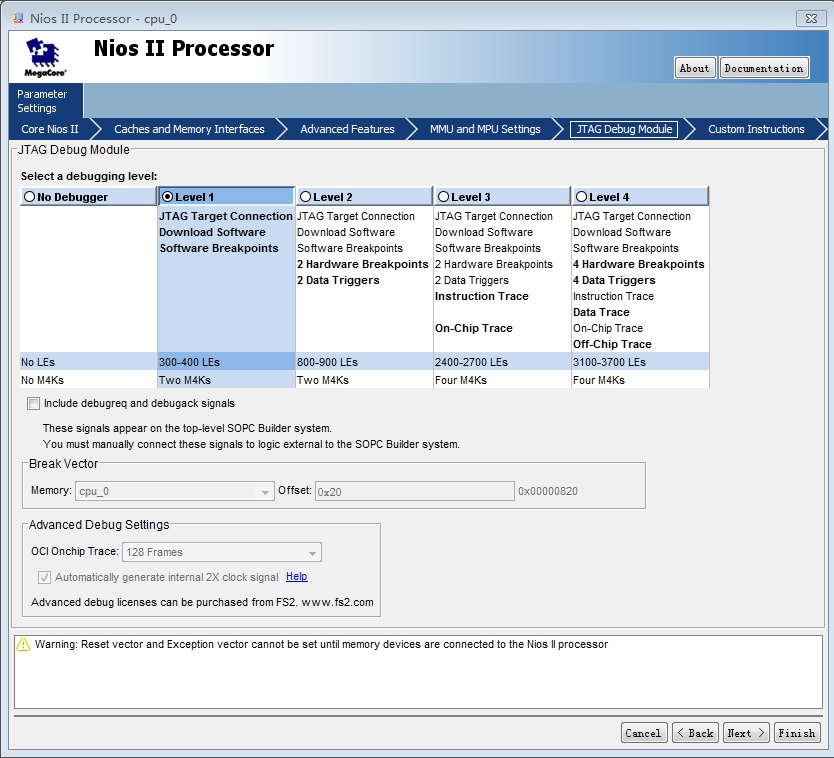

单击 ,出现下图对话框,显示的是

,出现下图对话框,显示的是 选项卡,指定下列设置:

选项卡,指定下列设置:

不选中

不选中

单击 ,直到出现如下对话框,显示的是

,直到出现如下对话框,显示的是 选项卡,不改变其中设置。

选项卡,不改变其中设置。

为了方便调试,给CPU加入JTAG调试模块。本实验选择“Level 1”,支持软件断点调试。

单击 ,出现

,出现 选项卡,该选项卡用于设置用户定制的指令。本实验不使用用户指定的指令,不改变其中的设置。

选项卡,该选项卡用于设置用户定制的指令。本实验不使用用户指定的指令,不改变其中的设置。

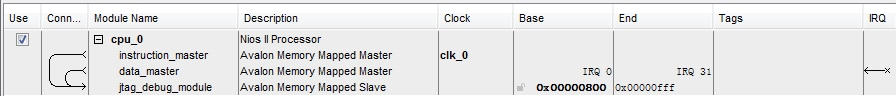

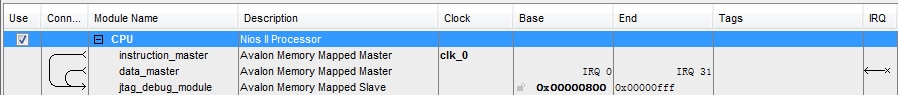

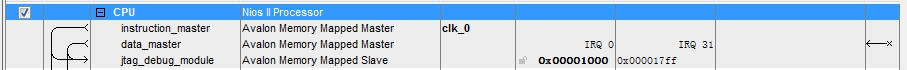

单击 完成Nios II处理器的配置,生成一个带JTAG调试接口的Nios/s型CPU核。在激活的元件窗口中将出现名称为cpu_0的Nios II内核,右击激活元件窗口中名为cpu_0的Nios II内核,然后选择Rename,将其命名为CPU.

完成Nios II处理器的配置,生成一个带JTAG调试接口的Nios/s型CPU核。在激活的元件窗口中将出现名称为cpu_0的Nios II内核,右击激活元件窗口中名为cpu_0的Nios II内核,然后选择Rename,将其命名为CPU.

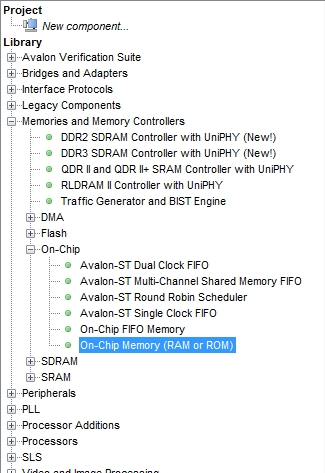

(4)添加片内存储器

处理器系统至少要求一个存储器用于数据与指令。

本实验设计一个2KB片内ROM存储器用于存储程序代码;1KB片内RAM存储器用于变量存储。

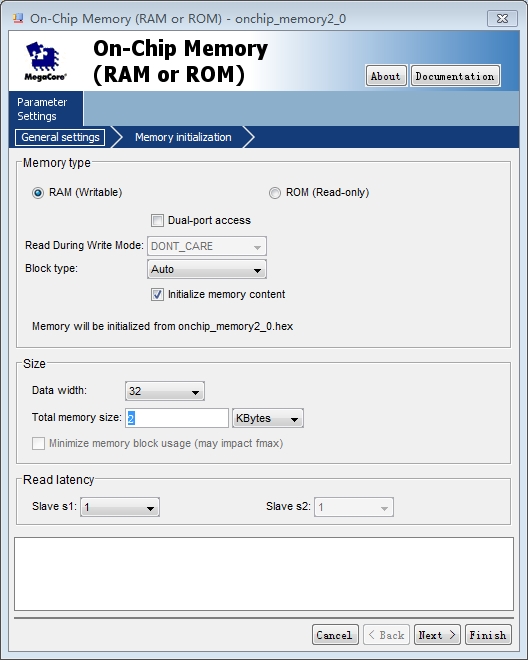

如上图,双击 ,出现片内存储器配置向导,具体配置如下图:

,出现片内存储器配置向导,具体配置如下图:

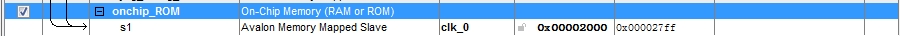

不要改变其他任何默认设置,单击 ,在激活元件窗口中出现名称为onchip_memory_0的片内存储器,右击激活元件窗口中的onchip_memory2_0,然后选择Rename将onchip_memory2_0重命名为onchip_ROM。

,在激活元件窗口中出现名称为onchip_memory_0的片内存储器,右击激活元件窗口中的onchip_memory2_0,然后选择Rename将onchip_memory2_0重命名为onchip_ROM。

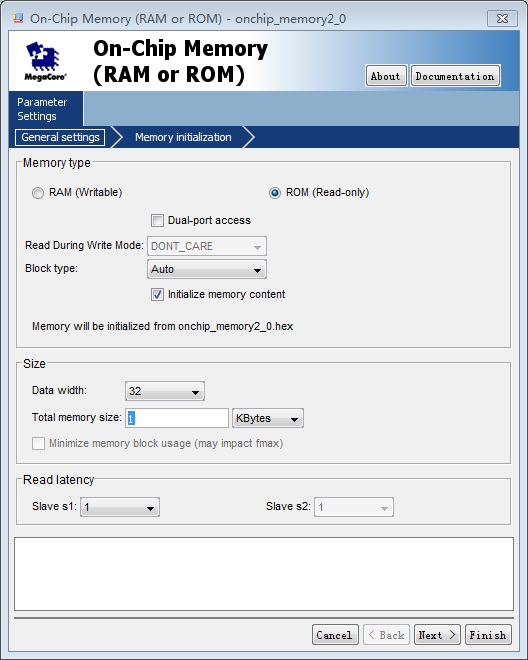

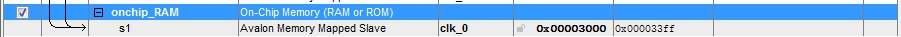

采用同样的方法添加1KB的onchip_RAM。

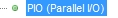

(5)添加PIO

如下图,双击

出现 配置向导,具体设置如下图:

配置向导,具体设置如下图:

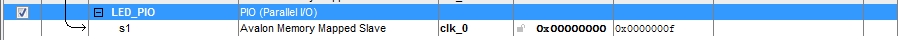

单击 ,在激活元件窗口中出现名称为pio_0的PIO,右击激活元件窗口中的pio_0,然后选择Rename将pio_0命名为LED_PIO。如下图:

,在激活元件窗口中出现名称为pio_0的PIO,右击激活元件窗口中的pio_0,然后选择Rename将pio_0命名为LED_PIO。如下图:

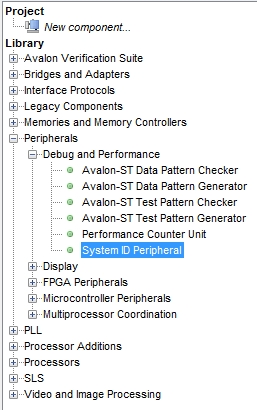

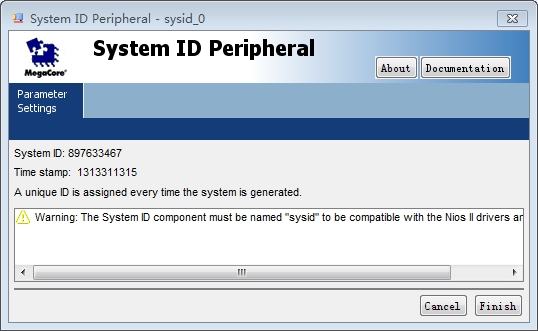

(6)添加系统ID外设

如下图,双击

如下图,单击

将sysid_0重命名为sysid

(7)指定基地址和中断请求优先级

单击System下的Auto-Assign Base Addresses和Auto-Assign IRQs命令,简单分配外设基地址和中断优先级

(8)设置Nios II复位和异常地址

双击

出现下图对话框,将 的

的 设置为onchip_ROM。

设置为onchip_ROM。

将 的

的 设置为onchip_RAM。

设置为onchip_RAM。

如下图:

(9)生成Nios II系统

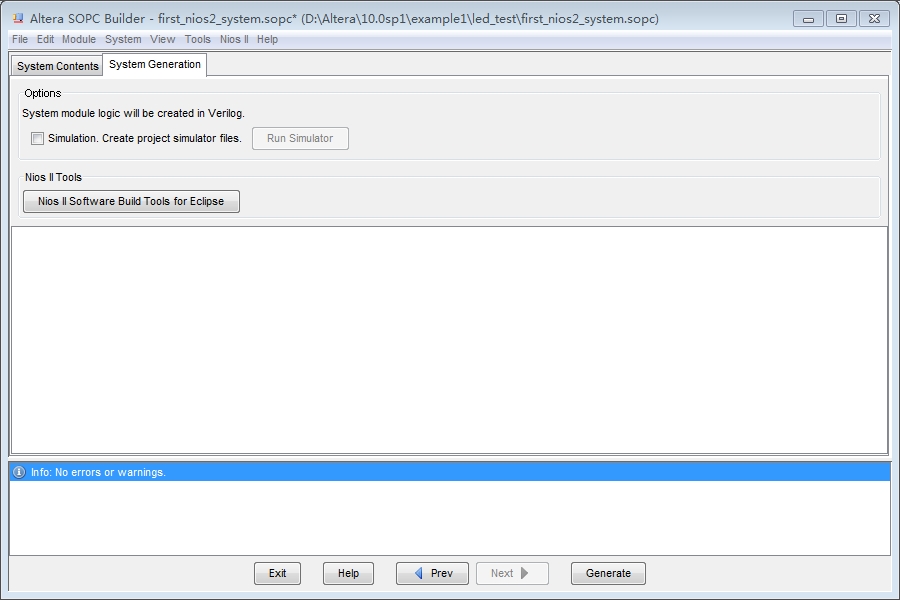

选择 选项卡,如下图

选项卡,如下图

单击 ,系统生成开始

,系统生成开始

单击 退出并返回到Quartus II软件

退出并返回到Quartus II软件

3)集成Nios II系统到Quartus II系统

(1)添加Nios II系统模块到Quartus II顶层模块

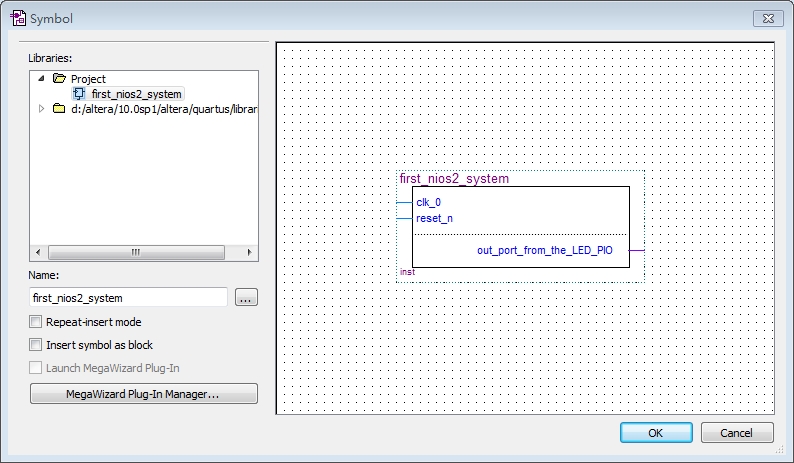

进入Quartus II中,在led_test.bdf窗口的任意处双击,弹出添加符号对话框。

具体操作如图:

单击 ,防止该符号

,防止该符号

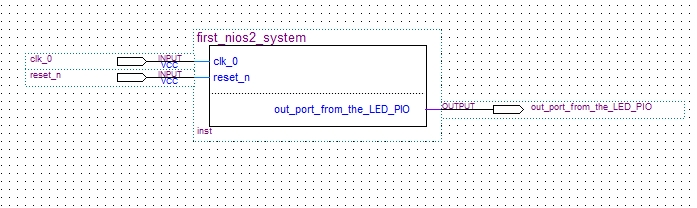

(2)添加引脚和其他基本单元

右键单击该符号,单击Generate Pins for Symbol Ports添加引脚,如下图:

选择File——Save保存BDF文件

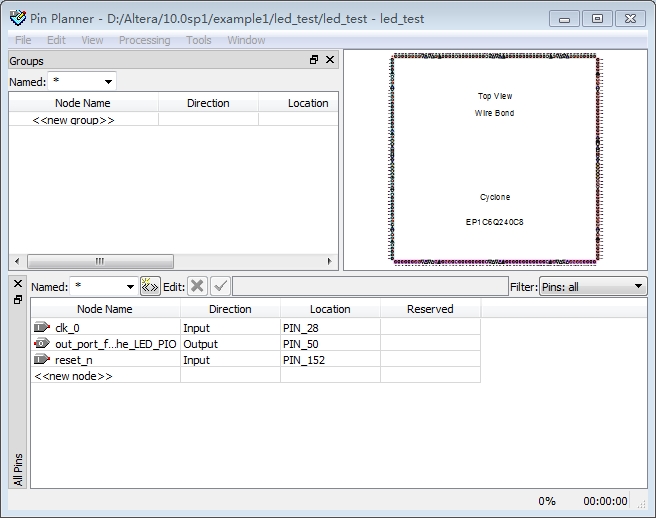

(3)分配FPGA引脚

单击 按钮启动全编译

按钮启动全编译

选择Assignments——Pin Planner打开引脚分配对话框,具体分配如下图

单击 按钮再次启动全编译

按钮再次启动全编译

(4)器件和引脚的其他设置

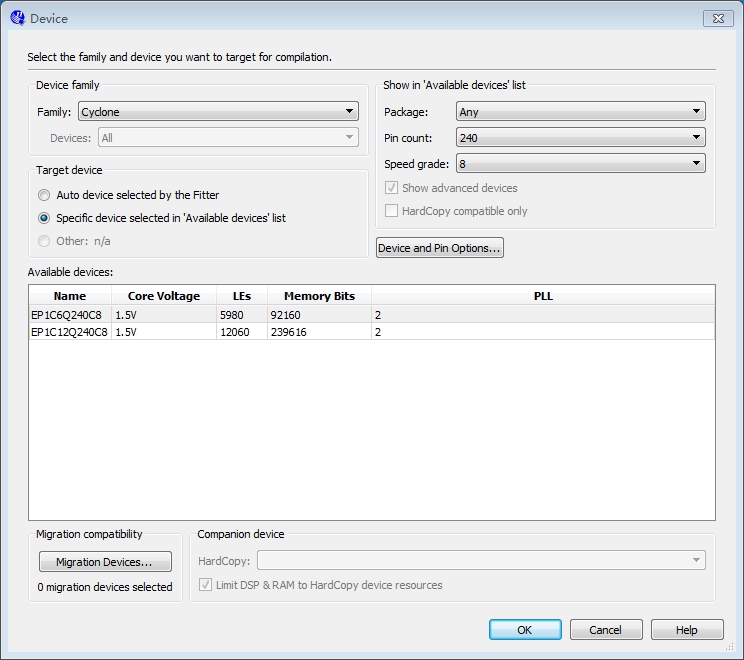

单击Assignments目录下的Device,弹出Device对话框,如下图:

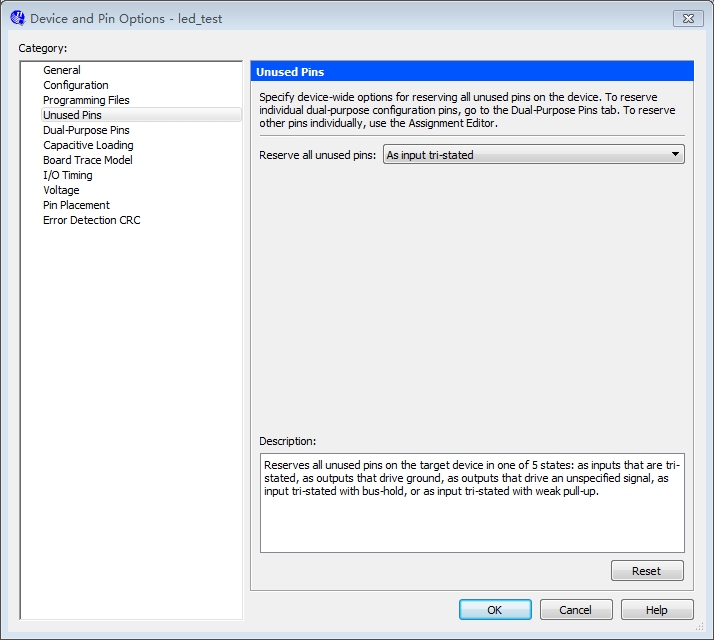

单击 ,打开

,打开 对话框,选择Unused Pins选项卡进行未使用引脚的设置,将未使用的引脚设置为高阻输入,如下图:

对话框,选择Unused Pins选项卡进行未使用引脚的设置,将未使用的引脚设置为高阻输入,如下图:

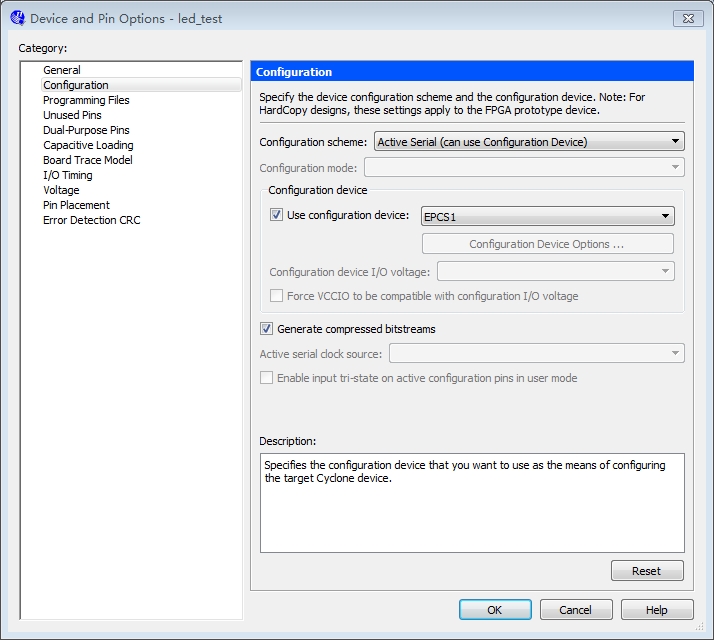

选择Configuration选项卡按下图设置,即采用串行配置器件EPCS1的主动配置:

点击OK两次,单击 进行全编译

进行全编译

4)下载硬件设计到目标FPGA

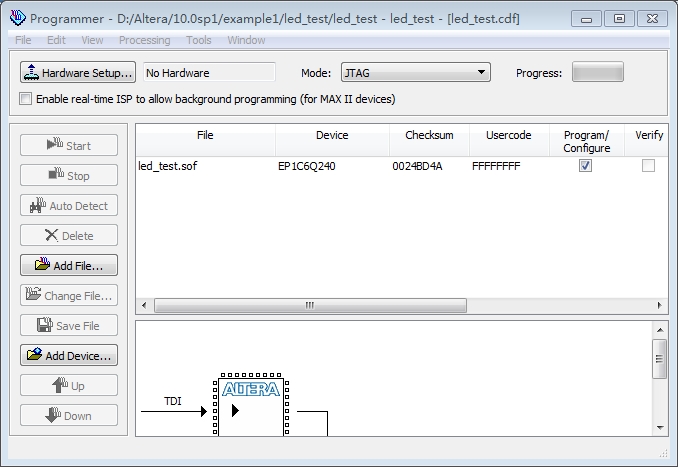

单击 ,打开编程器窗口,如下图:

,打开编程器窗口,如下图:

单击 开始使用配置文件对FPGA进行配置。

开始使用配置文件对FPGA进行配置。

/3

/3

文章评论(0条评论)

登录后参与讨论