我们在设计中使用了AD9235采样率40M,12bit的AD芯片,在实验板上输入固定为21.4M,测试AD9235的信噪比在40db左右,离AD官方测试板的指标和12bitAD能够达到的理论信噪比还有较大的距离,设计需要信噪比达到60db,现针对我们实验板的AD周边电路存在的问题进行了改进。

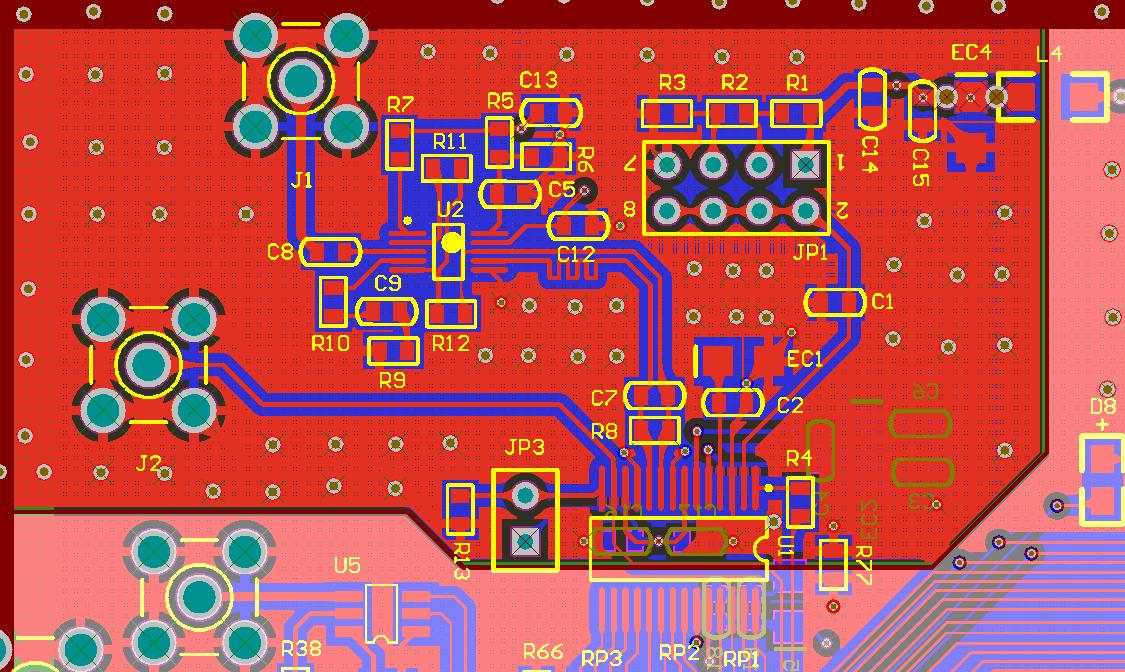

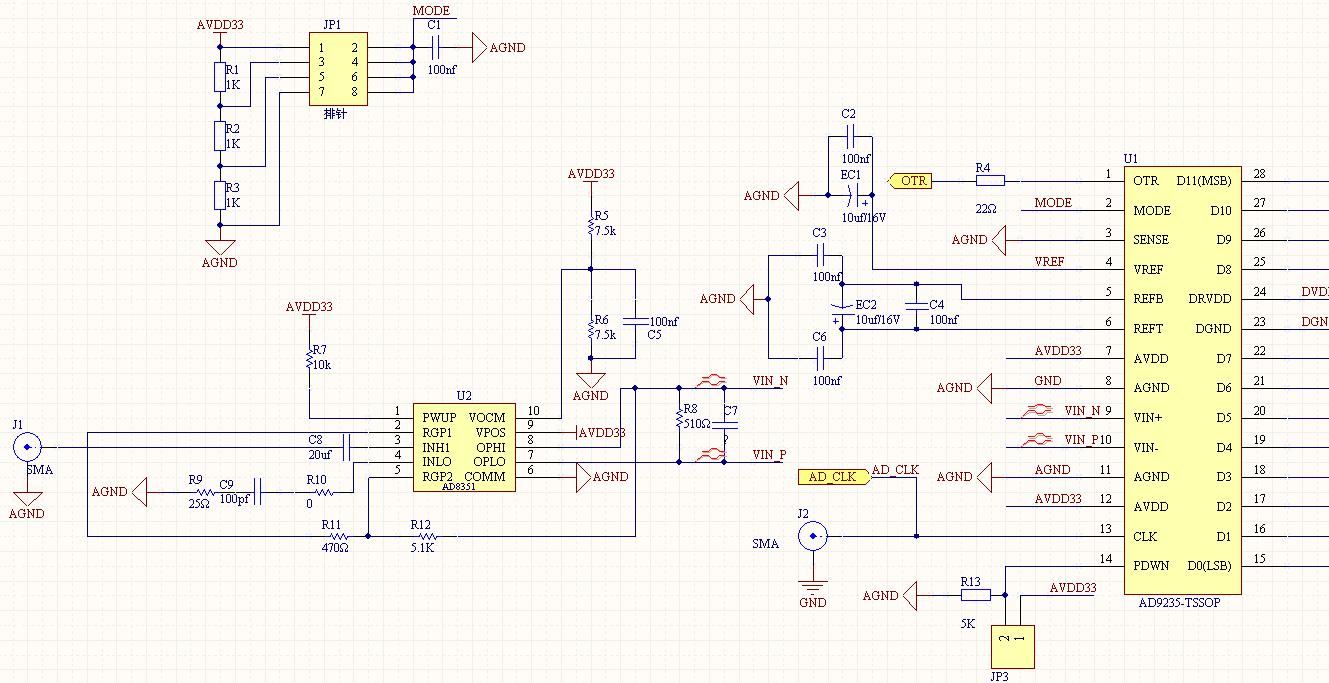

实验板处于系统原理实验阶段,在很多地方都存在不足之处,原理图和PCB如下图所示,对AD信噪比有影响的具体有以下几个部分:

1. AD9235和前端驱动AD8351的电源来自于FPGA的3.3VIO供电,只是加了磁珠和电容滤波,噪声有可能从电源部分引入信号导致信噪比降低。

2. AD9235的时钟使用的是FPGA内部DCM分频产生的30M时钟,时钟的精度大于100PPM,抖动估计也在100PS以上,AD时钟的抖动会造成孔径抖动,会降低信噪比。

3. PCB布线时将AD9235的电和地都按照数字电、地和模拟电、地严格分开,并不利于信噪比的提高。

根据以上问题,对于新的开发板进行了以下几处改进:

1. AD9235和前端驱动AD8351的电源使用低噪声的LDO单独供电,降低电源部分的噪声。

2. AD9235的时钟输入采用高精度、低抖动的硅晶振提供,精度可以达到10PPM,抖动可以达到1PS。

3. PCB设计时应该把AD9235当做模拟器件来看,将AD9235的地统一连接,都按模拟地处理,数字电和模拟电都是用模拟的3.3V电,只是数字电用个磁珠进行隔离。

以上三处改进可以一定程度上的提高输出信号的信噪比,不过还有如下几个疑问:

1. 不知道上诉方法还有什么考虑不周的地方,还有没有其他更好的改善输出信噪比的方法。

2. 改进1中使用的低噪声LDO可否推荐一款,用MAX1117-3.3觉得不靠谱,打算选择ADP3338。

3. 新的PCB使用四层板,有没有更好的接地和布线建议。

/3

/3

bitao1983_395643617 2012-6-1 10:08

用户1667688 2012-4-9 22:01