作为FPGA工程师来说,碰到新的问题是设计中最常见的事情了,技术发展趋势日新月异,所以经常会有新的概念,新的需求,新的设计等待去实现。不是每个通过BAIDU或者GOOGLE都有答案。

因此,新的设计经常会有,那如何实现?

假设,FPGA需要设计一个接口模块,那我们就需要了解一下几个问题:

(1) 同步接口还是异步接口模块;

(2) 有哪些信号,功能是什么?

(3) 信号之间时序关系是什么?

(4) 传递的效率能够达到多少;

(5) 等等!

谁会给予这些答案,有一个好的tutor就是“datasheet”,一般来说FPGA设计一个接口模块,必然与其他硬件电路进行连接。

假如是外部连接接口为总线接口,那至少包括却不限于以下信号,

(1) 地址:能够支持的最大地址空间,数据和地址是否复用接口;

(2) 数据:一般读数据和写数据复用同一接口,一般数据信号此时都为三态。三态信号有OE信号。

(3) 读写命令。单次的读操作、单次的写操作

(4) 是否支持突发传输,burst的读写操作

(5) 同步还是异步。

(6) 控制信号之间的相位关系及建立保持时间的要求。

图为 TI 系列35X系列处理器的GPMC的接口,由图中可以看出其时钟、地址、数据等操作信号。

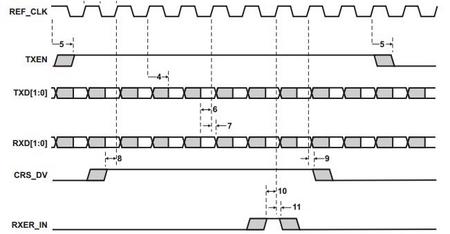

如果是同步并行接口,一般用于数据流传输,如AD/DA的输入或输出,网口PHY的输出信号等,一般的同步并行信号,通常包括,(1)时钟信号、(2)数据、信号(3)使能信号等。

上图为RMII的数据接口,图中可以看到其控制信号,数据信号及使能信号。作为流传输接口,一般可以支持双向双工传输。上述两种接口描述了两种主流的FPGA的外部接口,即总线接口和流传输接口。通过软件定义和FPGA内部逻辑设计,总线接口可以实现流的传输(总线接口实现双向传输,可以通过轮询和中断两种方式实现),同时流传输接口也可以实现总线读写功能。可以根据具体的使用环境进行设计。

上图为RMII的数据接口,图中可以看到其控制信号,数据信号及使能信号。作为流传输接口,一般可以支持双向双工传输。上述两种接口描述了两种主流的FPGA的外部接口,即总线接口和流传输接口。通过软件定义和FPGA内部逻辑设计,总线接口可以实现流的传输(总线接口实现双向传输,可以通过轮询和中断两种方式实现),同时流传输接口也可以实现总线读写功能。可以根据具体的使用环境进行设计。

SERDES接口则是另一种数据流的传输接口, 现在FPGA的serdes最高可以支持到28Gbps。实际上为了满足减少板级连线,并且提高传输速率的需求。集成更多的SERDES也是FPGA发展的趋势。

上图为SERDES的框图,由PCS和PMA模块构成,PMA一般为硬核IP,PCS为软核或者硬核模块,收发独立,且都为差分信号(serdes将在后续章节详述)。值得一提的是,SERDES接口对FPGA逻辑的接口一般固定位同步并行接口,数据信号位宽都较大。

这些接口如何做详细设计,一方面可根据其上述共性特点,这能够对其特点有大概的认识,另一方面则是FPGA连接的器件的DATASHEET。根据这些器件接口功能的描述和支持的特性。FPGA可根据需要和功能特性,进行有选择的实现(例如总线接口不需要brust操作,则可只实现单次的读写,就可以满足业务的需求,进行功能裁剪和简化等等)。

接口设计完成,FPGA就要对设计进行基本测试。对于流接口来说,能够支持环回的功能的话(即将收到数据流再发回),就极大方便测试。对于总线接口则需要支持对FPGA内部某地址的读写操作的测试。这就属于可测性设计的范畴。(后续将专题详述FPGA的可测性设计)。

如果一个模块没有任何的输入输出,其再复杂的功能也等同一块石头,或者只有输入,没有输出也等同一块石头。因此输入和输出则是一个设计的第一步。

/1

/1

用户1726050 2015-7-14 16:41