当下,最火的学问莫过于《大数据》,大数据的核心思想就是通过科学统计,实现对于社会、企业、个人的看似无规律可循的行为进行更深入和直观的了解。FPGA的可测性也可以对FPGA内部“小数据”的统计查询,来实现对FPGA内部BUG的探查。<?xml:namespace prefix = o />

可测性设计对于FPGA设计来说,并不是什么高神莫测的学问。FPGA的可测性设计的目的在设计一开始,就考虑后续问题调试,问题定位等问题。要了解FPGA可测性设计,只不过要回答几个问题,那就是:

(1) 设计完成如何进行测试?

(2) 设计出现问题,如何迅速定位?

(3) 如何在设计之初就能划分故障的层次,进行问题隔离?

一般情况下,在设计的调试阶段,如果出现BUG,则需要通过嵌入式逻辑分析仪(chipscope/signaltap)对可能出现问题的信号进行抓取。这种方式,对于较大型的设计调试速度较慢(其编译时间较长,迭代速度较慢,但是也是一种很有效的手段和FPGA的必备技能)。那么对于大型工程的可测试性,有什么行之有效的手段?

(1)统计计数。

FPGA设计中的统计计数不是不是什么《大数据》,只不过是些“小数据”,例如,对于网络接口来说,收到多少包,发送多少包,收到多少字节,发送多少字节。 对于一个模块来说,收到多少次调用,或者发起多少次操作。对于读取FIFO的数据流操作,从FIFO中读取多少frame(帧),向后级FIFO写入多少帧。

这些计数,毫无疑问都是需要占用资源的,但是占用这些资源是有价值的。通过这些计数,设计可以通过总线接口供外部处理器读出。于是一张FPGA内部设计的“大数据”图形就显现出来了”。

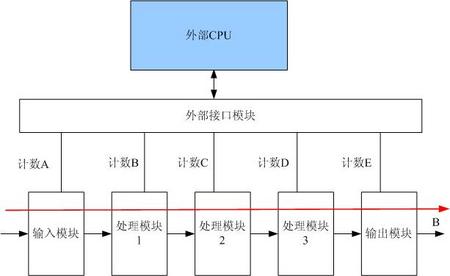

从上图可得,通过外部CPU可将各处理模块中的计数,分别读出,于是得到其内部的一张数据流图。我们可以简化设计为(计数A->计数B->计数C->计数D->计数E)。实际使用中可根据占用的资源和实际需要的观测点来确定。

从上图可得,通过外部CPU可将各处理模块中的计数,分别读出,于是得到其内部的一张数据流图。我们可以简化设计为(计数A->计数B->计数C->计数D->计数E)。实际使用中可根据占用的资源和实际需要的观测点来确定。

假设,我们在调试过程中发现,有输入突然没有输出,这是不需要再去内嵌逻辑分析仪来抓取信号,通过CPU的软件,可以打印出所有计数,在有输入驱动的情况下,假设计数C有变化,而计数D没有变化,则直接定位处理模块3,此时处理有问题,简单直接而有效。

令一种情形也可以迅速定位,输入多,但是输出少,比如正常输入的码流,但是输出到显示上确实缺帧少帧,完全不流畅。通过计数分析,原本帧计数C和D应该一样多,但是D却计数较C少很多,说明此时处理模块3性能不够,或者设计有缺陷。这样就把整个设计的关键点定位到处理模块3.

通过FPGA内部各模块的关键计数分析,来定位分析问题,在设计上没有任何难度。不过需要外部CPU或者FPGA嵌入式CPU的配合使用。

凡事有利就有弊,添加多的计数,会增加资源的使用量,那么如何平衡?对这种分析计数进行单独位宽设定,在全局统一的宏定义中定位`define REG_WIDTH N 。此时N的设定可以灵活多样,8位/16位/32位等等。可以根据项目中资源的剩余量,灵活添加所需的逻辑,毕竟这些计数的值提供分析试用。

(2)状态输出。

如果向上述问题一样,我们定位到某个模块,那么如何再定位到模块中那个逻辑的问题?

解决这个问题的关键,就是状态机,向输出计数一样,一般的设计中,都会以状态机为核心进行设计,将状态机的CS(当前状态)信号引出,如果没有外部输出的情况下,当前状态应该为IDLE。比如上文中,我们定位到模块3此时死机,等待不再输入外部信号时,此时模块3中的状态机信号如不为IDLE,假如此时正处于状态 B_CS,则说明此时模块的错误出现在状态B。而B跳转必须由信号X起效。因此可以直接定位到信号X的问题。剩下就是要定位信号X为什么不起效。(也许你看看代码就能知道**不离十,是不是一秒钟变高手! 开个玩笑!)

(3)逻辑复位。

划分FPGA的问题或者模块问题的另一种方式就是逻辑复位,上文讲复位时(架构设计漫谈),逻辑复位,如果A模块自身有逻辑复位,如果设计没有输出(通俗叫做“FPGA死了”),如果怀疑某个模块,该模块逻辑复位后,设计又正常工作,则需要定位的则是可以是该模块、或者该模块影响的与其连接模块(该模块的非正常输出导致下一级模块出错)。

本文将的FPGA可测性设计,非ASIC讲的通过插JTAG/BIST进行的测试。其目的还是通过关注如何测试的设计,来定位问题,提高FPGA的可测性。除此之外,逻辑探针也是可以一个解决测试问题的方向(专题另述)。可测性的提高,意味着调试手段的增加,调试速度加快,而不是一味的依赖嵌入式逻辑分析仪。能够达到快速问题定位能力,是FPGA研发能力一个重要的体现,而可测性设计则是提升这一能力有力的助手。

/2

/2

用户377235 2014-7-31 13:11

用户1646474 2014-7-24 10:04