特权同学,版权所有

配套例程和更多资料下载链接:

http://pan.baidu.com/s/1jGjAhEm

连接好下载线,给SP6开发板供电。

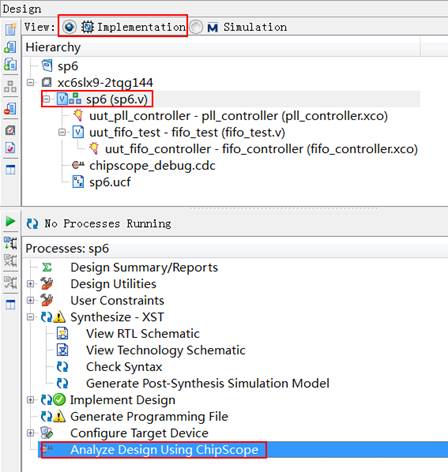

如图所示,在“Design à Implementation”界面下,首先选中“Hierarchy”下的“sp6.v”文件,接着双击“Processes: sp6”下的“Analyze Design Using ChipScope”。

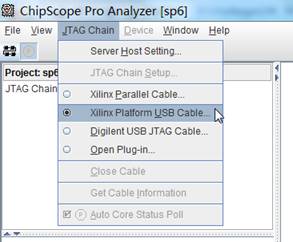

在“ChipScope Pro Aanlyzer”界面中,点击菜单“JTAG Chain à Xilinx Platform USB Cable…”。

随后弹出如图所示界面。大家可以尝试点击“Blink Cable LED”,相应的下载线上的LED将会闪烁,说明下载线连通正常。最后点击“确定”。

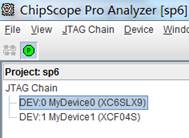

此时,我们看到“Project”界面下出现了两个设备,如图所示。选择第一个设备。

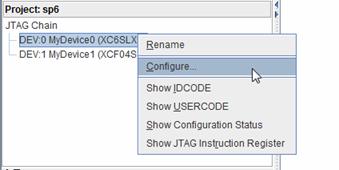

在第一个设备上单击鼠标右键,如图所示,选择“Configure…”。

接着弹出的配置界面中,点击“Select New File”,弹出右侧所示界面定位到当前工程所在文件夹下的sp6.v文件。完成后,点击OK。

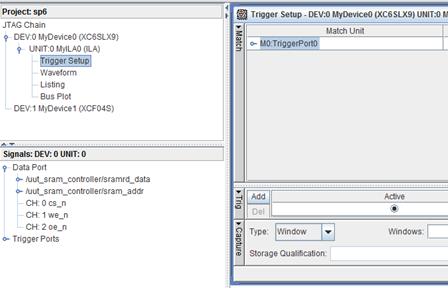

此时,如图所示,我们可以双击“Trigger Setup”进行读写触发条件的设置,建议大家使用我们已经设定好的触发条件即可。

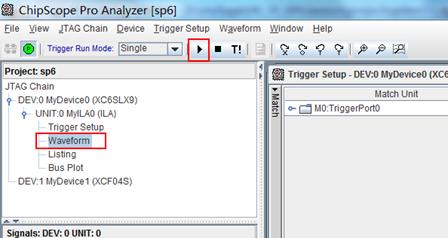

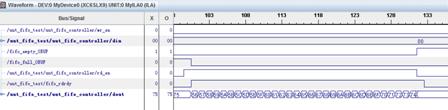

如图所示,我们单击菜单栏上的运行图标,然后双击“Waveform”查看波形。

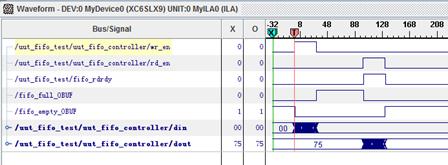

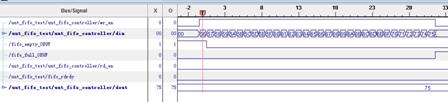

我们设定触发条件为FIFO写使能信号上升沿时采样波形,采集到的波形如图所示。

/5

/5

文章评论(0条评论)

登录后参与讨论