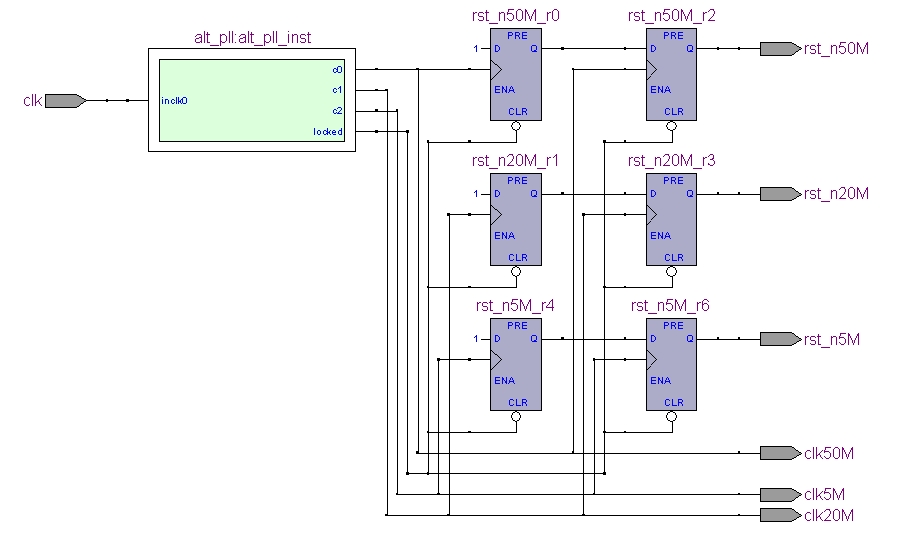

module pll_ctrl(

clk,

clk50M,clk20M,clk5M,

rst_n50M,rst_n20M,rst_n5M

);

input clk; //50M时钟输入

output clk50M; //PLL分频时钟输出

output clk20M;

output clk5M;

output rst_n50M; //异步复位信号产生

output rst_n20M;

output rst_n5M;

//****************例化PLL**********************

alt_pll alt_pll_inst (

.inclk0 ( clk ),

.c0 ( clk50M ),

.c1 ( clk20M ),

.c2 ( clk5M ),

.locked ( locked )

);

wire locked;

//**************50M复位信号产生********************

reg rst_n50M_r0,rst_n50M_r2;

always @ (posedge clk50M or negedge locked)

if(!locked) rst_n50M_r0 <= 1'b0;

else rst_n50M_r0 <= 1'b1;

always @ (posedge clk50M or negedge locked)

if(!locked) rst_n50M_r2 <= 1'b0;

else rst_n50M_r2 <= rst_n50M_r0;

assign rst_n50M = rst_n50M_r2;

//**************20M复位信号产生*****************

reg rst_n20M_r1,rst_n20M_r3;

always @ (posedge clk20M or negedge locked)

if(!locked) rst_n20M_r1 <= 1'b0;

else rst_n20M_r1 <= 1'b1;

always @ (posedge clk20M or negedge locked)

if(!locked) rst_n20M_r3 <= 1'b0;

else rst_n20M_r3 <= rst_n20M_r1;

assign rst_n20M = rst_n20M_r3;

//**************5M复位信号产生*****************

reg rst_n5M_r4,rst_n5M_r6;

always @ (posedge clk5M or negedge locked)

if(!locked) rst_n5M_r4 <= 1'b0;

else rst_n5M_r4 <= 1'b1;

always @ (posedge clk5M or negedge locked)

if(!locked) rst_n5M_r6 <= 1'b0;

else rst_n5M_r6 <= rst_n5M_r4;

assign rst_n5M = rst_n5M_r6;

endmodule

图1-1 PLL系统时钟与复位 RTL视图

/3

/3

文章评论(0条评论)

登录后参与讨论