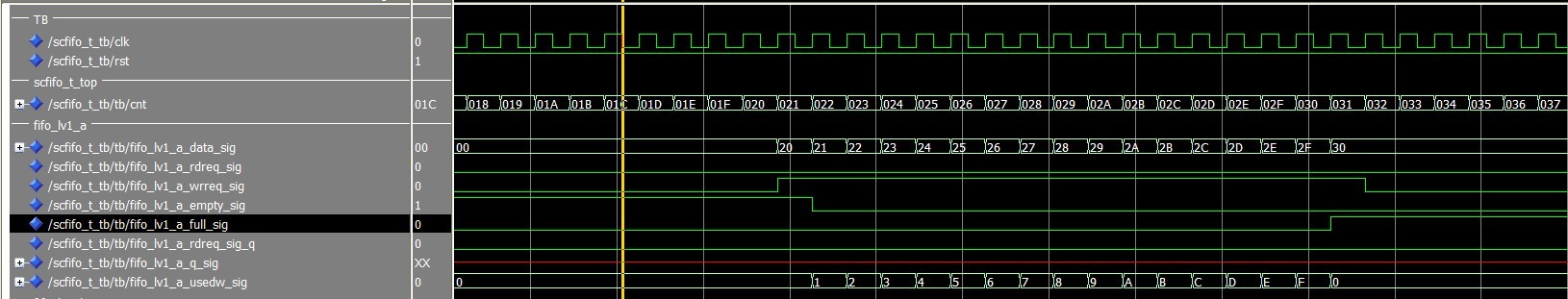

为了防止数据堵塞在FIFO里,所以不使用FIFO的almost empty和almost full来控制避免对满FIFO的写以及对空FIFO的读。假如简单的使用FULL信号来控制FIFO的写,那么就会出现如图1所示的对满FIFO的写操作,这样就会丢失一个数据。

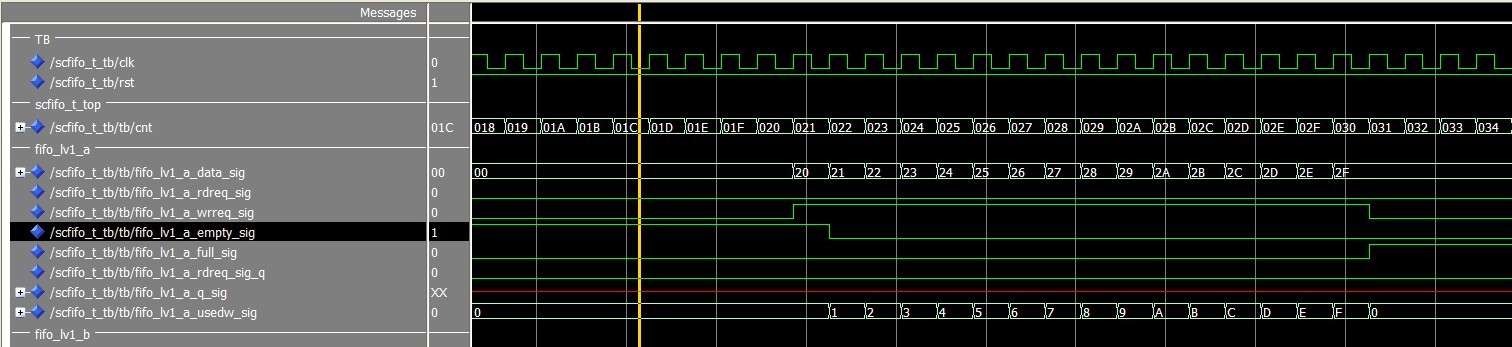

if cnt(5)='1' and fifo_lv1_a_full_sig='0' then fifo_lv1_a_wrreq_sig <= '1'; fifo_lv1_a_data_sig <= cnt(6 downto 0); else fifo_lv1_a_wrreq_sig <= '0'; end if;如果改成如下: if cnt(5)='1' and fifo_lv1_a_full_sig='0' and fifo_lv1_a_usedw_sig<15 then fifo_lv1_a_wrreq_sig <= '1'; fifo_lv1_a_data_sig <= cnt(6 downto 0); else fifo_lv1_a_wrreq_sig <= '0'; end if; 经过上述修改后(注意本例中的FIFO深度是16),当FIFO满了以后,逻辑会及时控制不往已经满了的FIFO里再写入数据了,效果如图2所示:

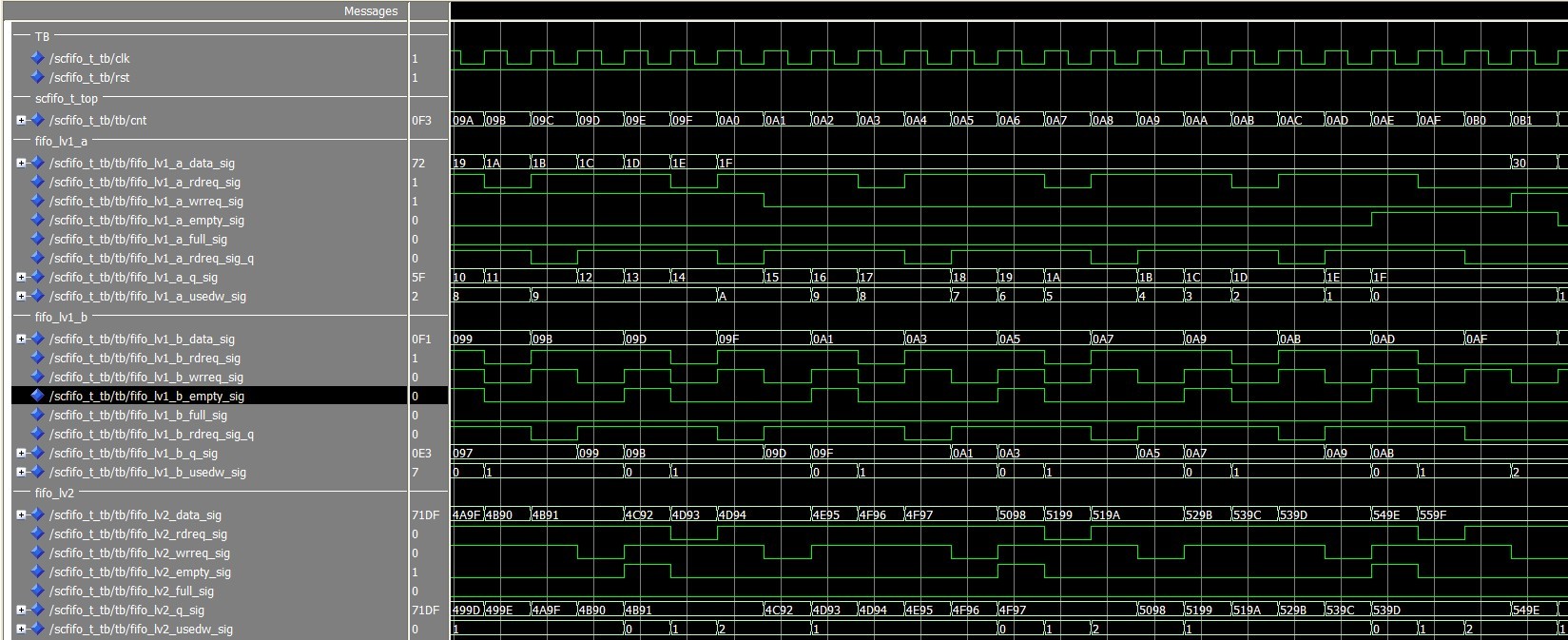

同样对于FIFO的读,也存在类似的情况,如果连续的从FIFO里弹出数据,当弹出最后一个数据的时候,FIFO会给empty信号置位,但是这个动作需 要一个时钟之后才能通知到user,所以这时候逻辑不会停止读,那么在user不知情的情况下就产生一个对空FIFO的读操作,如图3所示:

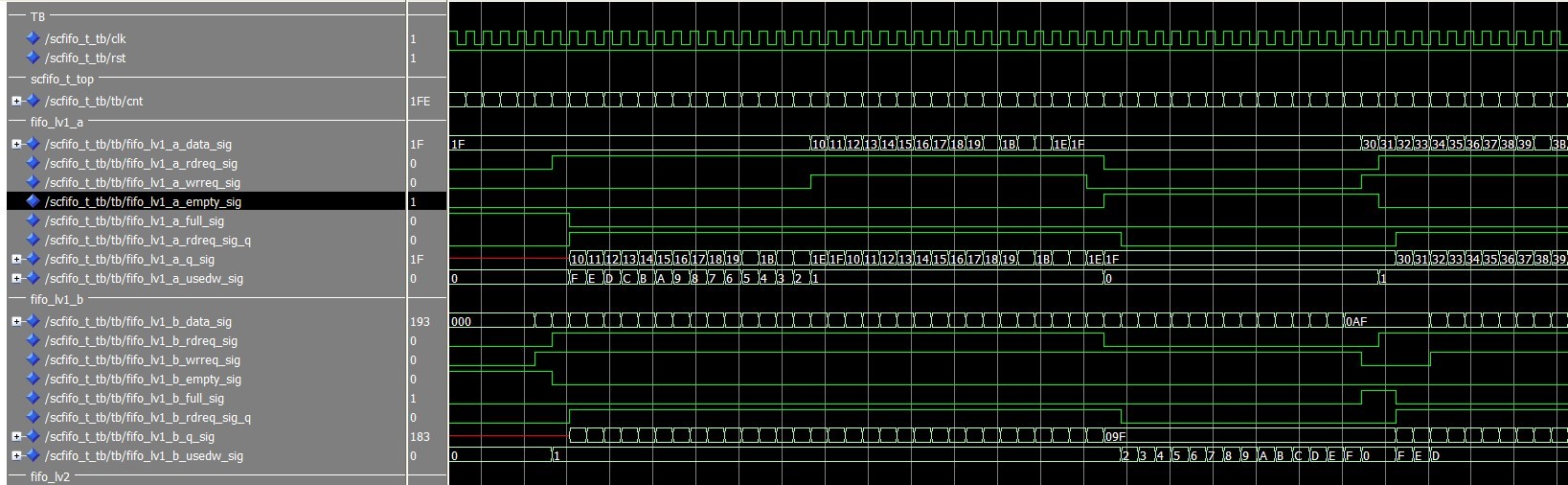

if ((fifo_lv1_a_empty_sig='0' and fifo_lv1_a_usedw_sig>0) or fifo_lv1_a_full_sig='1') and ((fifo_lv1_b_empty_sig='0' and fifo_lv1_b_usedw_sig>0) or fifo_lv1_b_full_sig='1') and fifo_lv2_full_sig='0' and fifo_lv2_usedw_sig<15 then fifo_lv1_a_rdreq_sig <= '1';fifo_lv1_b_rdreq_sig <= '1';else fifo_lv1_a_rdreq_sig <= '0';fifo_lv1_b_rdreq_sig <= '0'; end if;fifo_lv1_a_rdreq_sig <= '1' when ((fifo_lv1_a_empty_sig='0' and fifo_lv1_a_usedw_sig>0) or fifo_lv1_a_full_sig='1') and ((fifo_lv1_b_empty_sig='0' and fifo_lv1_b_usedw_sig>0) or fifo_lv1_b_full_sig='1') and fifo_lv2_full_sig='0' and fifo_lv2_usedw_sig<15 else '0';fifo_lv1_b_rdreq_sig <= '1' when ((fifo_lv1_a_empty_sig='0' and fifo_lv1_a_usedw_sig>0) or fifo_lv1_a_full_sig='1') and ((fifo_lv1_b_empty_sig='0' and fifo_lv1_b_usedw_sig>0) or fifo_lv1_b_full_sig='1') and fifo_lv2_full_sig='0' and fifo_lv2_usedw_sig<15 else '0';

图4 正确控制FIFO读,避免对已空FIFO误读

coyoo 2012-4-20 16:34

coyoo 2012-4-20 16:16

用户1000403 2012-4-18 11:01

用户1000403 2012-4-18 10:53

coyoo 2012-4-17 09:20

用户403664 2012-4-13 16:36

coyoo 2012-4-12 13:04