FPGA+MCU是一中非常流行的架构,MCU的并行总线在和FPGA通讯的时候一般都是异步的。

常见的MCU有单片机、ARM以及DSP等等,所谓的并行接口比如TI的TMS320C5410的HPI口。在FPGA加MCU的架构里往往存在着主控cpu地位的一片MCU,这一片MCU控制着众多节点的FPGA或者其他MCU等(比如通过背板或者其他总线比如CAN总线)。

走背板的话,由于常常背板走线比较长,所以信号反射比较严重,难以实现同步接口。如果使用异步接口,各个节点的FPGA内部可以轻松设计一个转换模块来是异步接口同步到内部系统时钟。

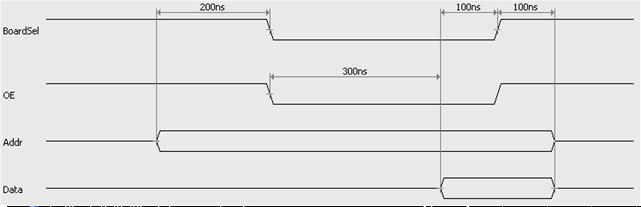

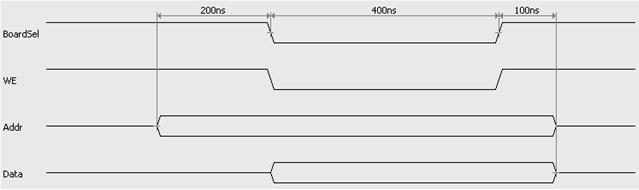

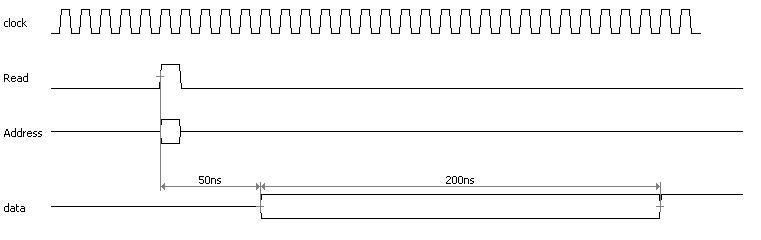

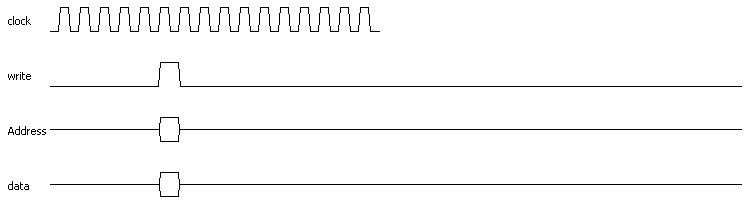

内部异步转同步模块,这是一个比较成熟技术,而且网上论坛讨论也比较多,这里不做介绍。这里直接给出一个实践例子,大家可以对照参考,图1和图2是异步时序,而图3和图4是对应的同步后的时序。

/3

/3

coyoo 2012-4-19 11:49

coyoo 2012-4-19 11:46

用户1605975 2012-4-18 10:10