前面有博文介绍了单个JTAG链上挂多个FPGA结构中如何应用Virtual JTAG进行项目调试,那么调试完成后就要将配置文件固化到配置芯片里,这里的配置芯片指的EPCS系列,当然可以直接将pof文件(注:由于是一片EPCS芯片配置多个FPGA,所以这里的pof文件是经过转换的pof文件)通过AS模式下载到EPCS芯片里。还有一种间接的方式就是通过在FPGA中例化flash loader经JTAG将配置信息烧写到EPCS配置芯片里,如果成功,那么在实际量产的时候就可以省略一个AS接口。

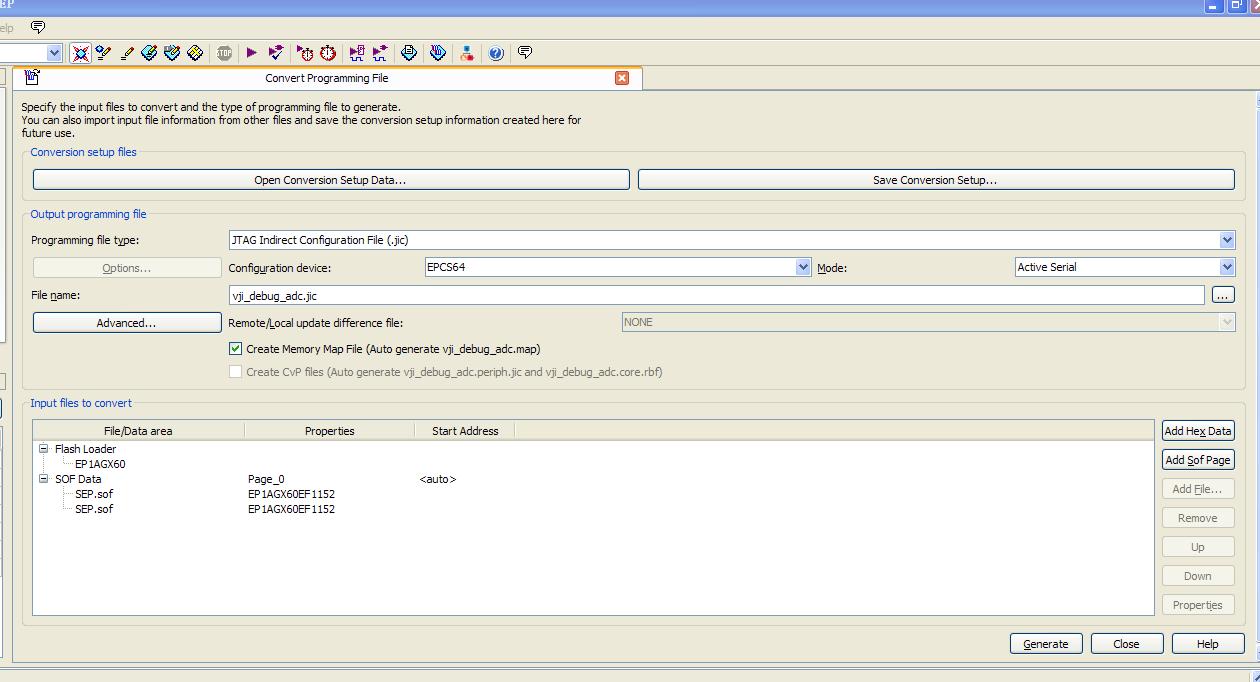

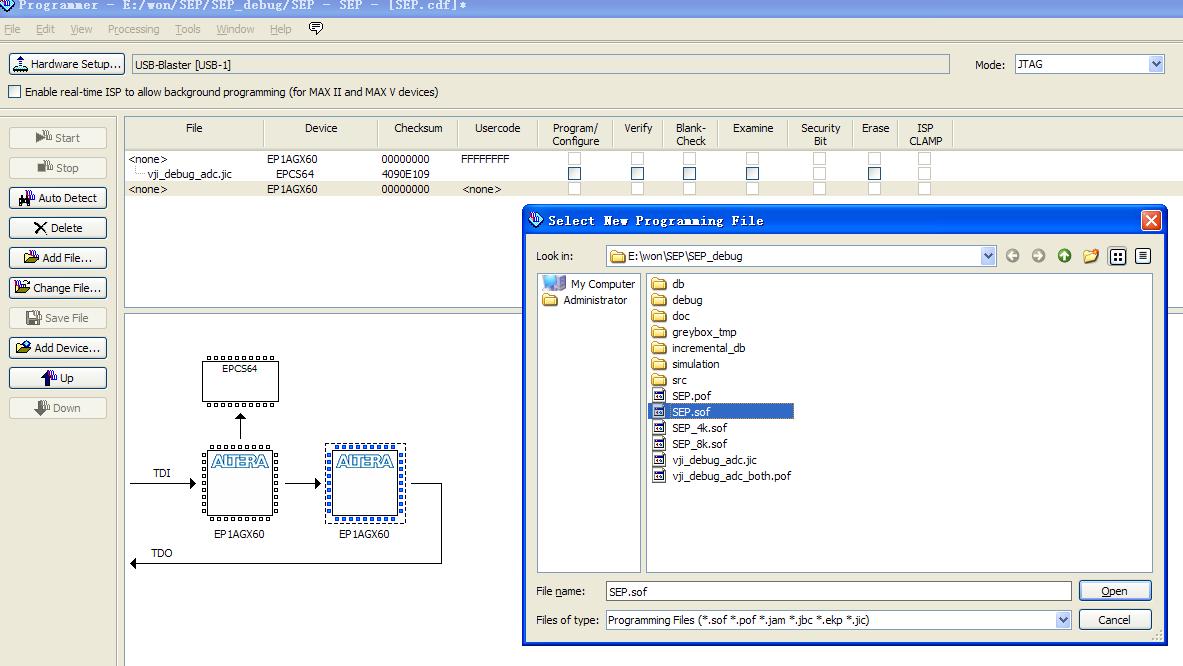

关于单链单FPGA的结构的情况,这里不做介绍,网上搜索一大堆,这里在此基础上介绍一个jtag挂多个FPGA结构如何生成jic并进行下载。图1是jic文件转换时的设置,跟单片时区别不大,唯一不同就是在SOF Data区域要加入多个sof文件。

图1 多个sof文件转换成jic文件

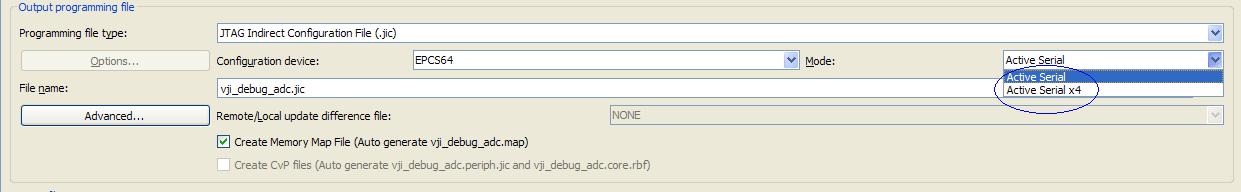

这里还需要提及的是在图1的JIC文件转换设置界面里,有个Mode设置项,可以选择“Active Serial x4”,图2所示。我选择的是x1模式,x4没有试过,应该对应的是快速AS加载模式。

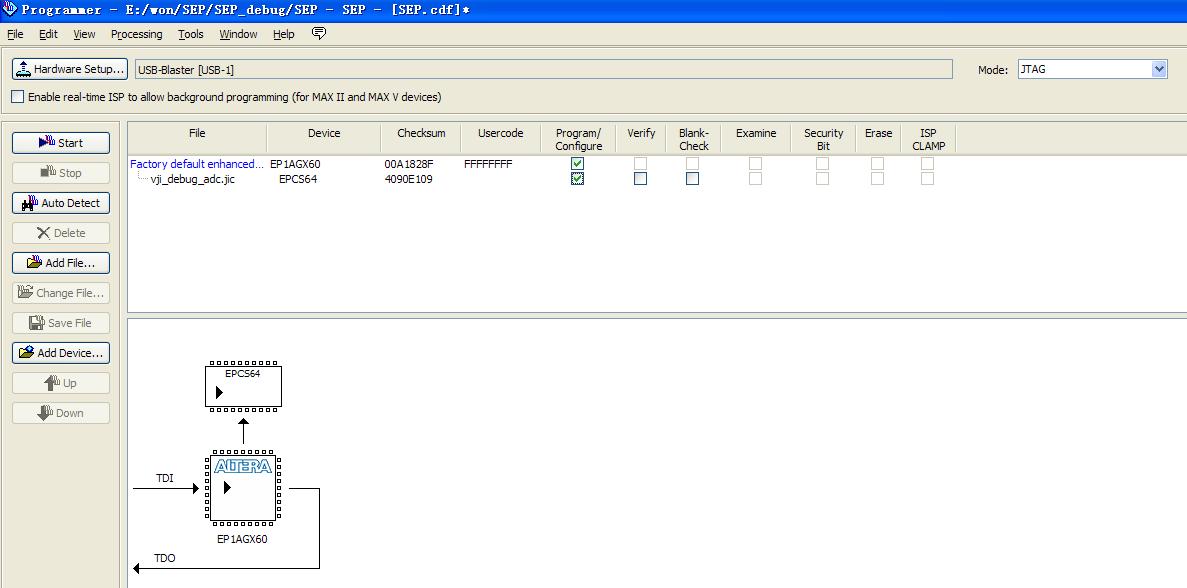

下面开始介绍如何下载jic文件到EPCS芯片中去,一开始我犯了一个错误,导致programmer给了我一个错误提示,并下载失败。我犯的错误如图3所示,即只单独在programmer里add了一个jic文件,如果这时候点击“start”就会报如下error:

Error (209031): Device chain in Chain Description File does not match physical device chain -- expected 1 device(s) but found 2 device(s).

图3 单JTAG链多器件结构单独add jic文件

实际上,这种结构在通过jtag下载sof文件的时候也不能只加载一个器件的sof必须链上所有器件的sof文件都下载进去,那么程序才能下载成功,因为硬件上所有器件的config_done引脚都接到一起了,所以链上任何一个器件未加载都会导致整个链路加载失败(因为configure done无法拉高)。

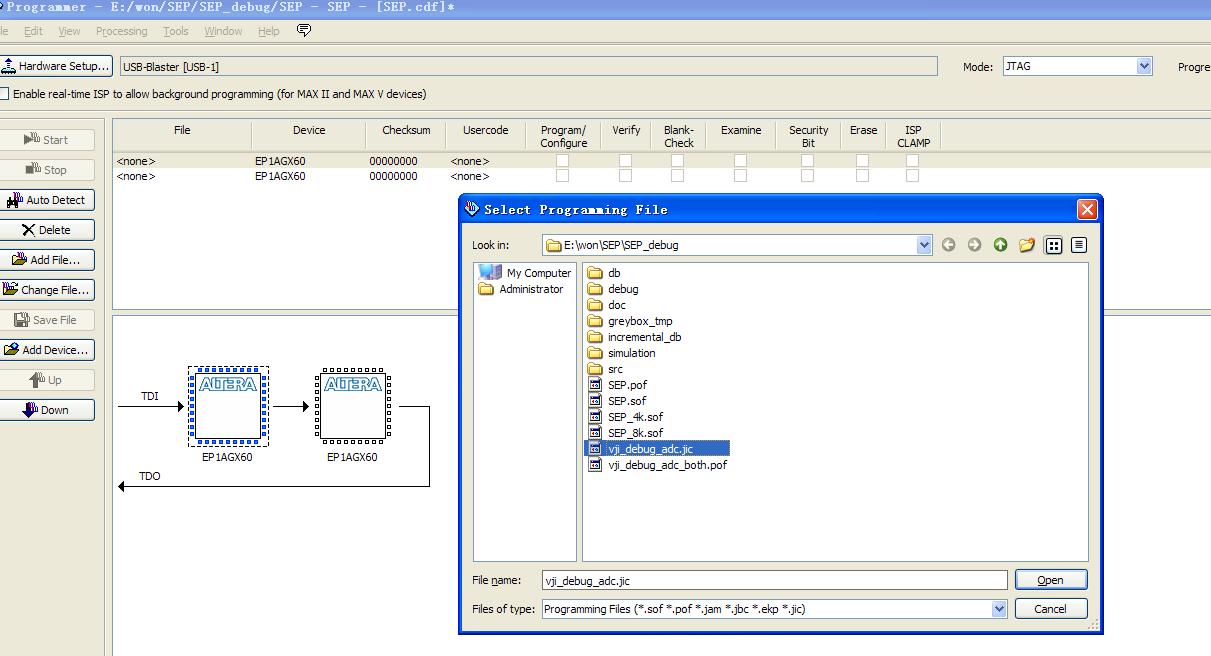

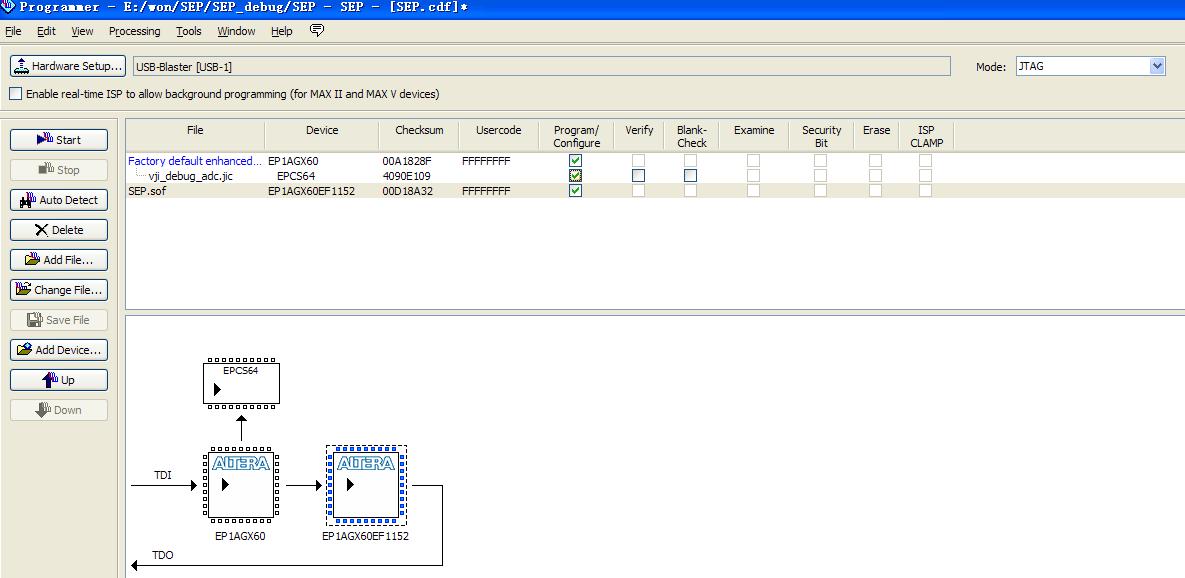

所以在烧写jic文件的时候必须象这种结构直接烧写sof文件那样,除了flash loader以外,其他所有器件也必须加载程序。图4显示了给链上第一片FPGA分配为flash loader,并为其加入JIC文件。

那么剩下的器件就加上任意可用的sof文件即可,反正也只是临时性的烧写进去,如图5所示。

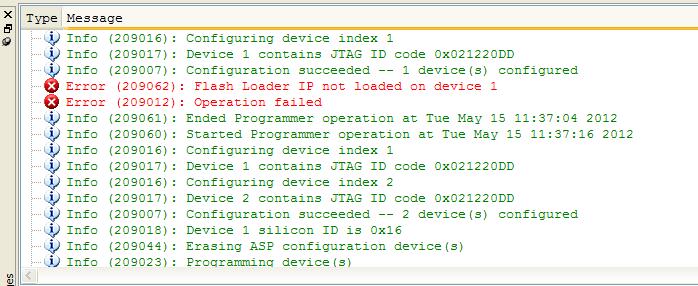

所有文件加入完毕后如图6所示,这个时候必须注意的是,就像前面所说的那样,必须所有器件同时加载,不然会导致下载失败,也即在“Program/Configure”这一列必须勾对所有选项,我做了个实验,就是只勾对jic对应的器件,下载后就会出现如图7所示的错误提示。

图6 JTAG链上所有器件加入配置文件完成

图7 单JTAG链多器件结构下只加下载flash loader的时候报错

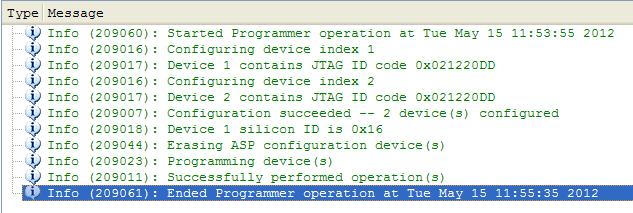

最后,按照图6所示设置好以后,点击“start”下载所有FPGA,以及烧写配置文件到EPCS配置芯片中,整个配置流程的信息如图8所示。

图8 整个下载过程的message

从上图我们发现整个下载过程耗时1分40秒,这里有个问题可以留给大家思考下,就是本博文介绍的是将第一片FPGA做为flash loader,那么第二片可否作为flash loader呢?!

coyoo 2014-4-8 20:20

用户1739054 2014-4-8 14:41

单链多FPGA(fpga不同类型)的.pof文件也是上述流程吗?

coyoo 2014-2-27 11:58

用户1738735 2014-2-26 21:10

用户1645455 2013-10-9 12:43

coyoo 2013-1-11 13:14

用户310504 2013-1-11 10:46