基于FPGA的TDC那些事之再谈粗时间

王敏志

概述

《基于FPGA的TDC那些事之粗细计数》一文中介绍了什么是粗计数和细计数,并阐述了在具体TDC设计中如何去实现。本文再次谈谈粗时间,主要想分析并解释笔者采用的粗时间计数器设计方法和较传统的方法的异同。

较常见的粗时间计数器设计

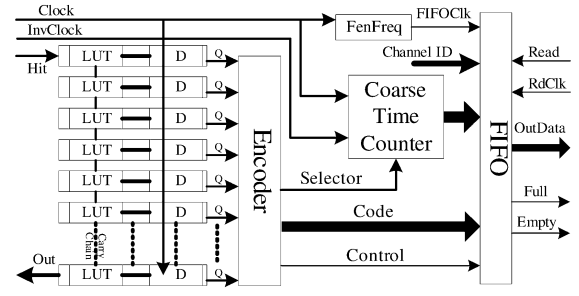

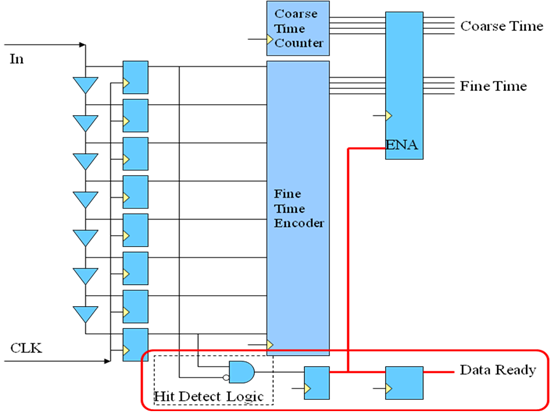

比较常用的粗时间计数方法在TDC系统中的位置如图1所示,我们的TDC系统架构基本与图1类似,主要的两点区别在于:一是不需要InvClock;二是Coarse Time Counter的控制信号不同,图1的控制信号是Selector,是一个根据Hit解码出来的选择信号。

图1:传统粗时间计数器在TDC系统中的位置

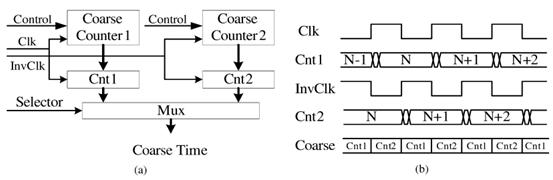

图2:Coarse Time Counter

图2是Coarse Time Counter的具体实现,(a)是该Counter的结构框图,所以有两个时钟来产生两个Counter,然后根据Hit到达的时间位于前半周还是后半周来选择哪一个Counter作为本Hit的Coarse Time Counter值。所以信号“Selector”是根据Fine Time测量结果产生的选择信号,可以很好的解决Hit和系统时钟之间的异步关系造成的粗计数器不稳定问题。

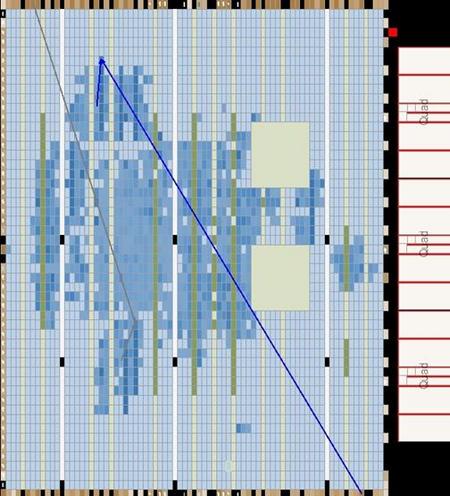

图3:Hit从FPGA的PIN到TDC的延时链走线

图3显示了Hit从FPGA引脚到延时链的走线距离,当然这是工具自动走线结果,实际也可以通过位置约束使距离尽量的近,不过这个引脚到延时链的走线延时时间为纳秒级别是无法改变的事实。所以才需要图2所示的Coarse Time Counter结构来解决这种uncertainty。

改进型粗时间计数器

在《基于FPGA的TDC那些事之粗细计数》一文中给出了改进型Coarse Time Counter具体实现的视图,如图4所示。

图4:改进型Coarse Time Counter具体实现

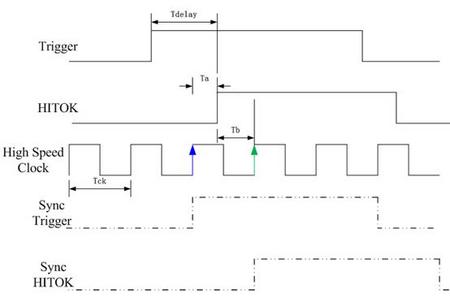

图4中的关键在于信号SQOK(即图5中的HITOK),这是一个标志Hit被延时链成功捕获的信号,且此信号是寄存器输出,符合时钟的建立保持时间,所以此后的逻辑设计都是基于pipeline的,这样就不存在所谓的uncertainty了。所以由于HITOK来“产生”Coarse Time Counter的值是合理的,稳定的。

图5

图6:改进型TDC架构

图6给出了改进型TDC的结构框图,由于Hit探测逻辑是利用了寄存器阵列的输出,也即使用的是同步后的信号进行Hit探测判决,所以判决条件满足了系统稳定所需的建立保持时间,所以Coarse Time Counter就不需要使用Gray码以及所谓的双计数器架构了。

结论

利用延时链“捕获”HIT巧妙设计出Hit探测判决输出,并用此信号控制Coarse Time Counter从而得到稳定的Coarse Time值,并简化了Coarse Time Counter的内部结构。

/3

/3

文章评论(0条评论)

登录后参与讨论