基于FPGA的TDC那些事之再谈细时间

王敏志

概述

TDC的Fine Time是TDC的实际测量结果,目前实现TDC最常用的方法就是内插法。所以延时线(Delay Line)必然成了TDC的核心部件,通过Delay Line来实现在一个时钟周期内插入N个延时单元,TDC通过输出HIT和相邻时钟沿之间延时单元数目来输出测量结果即Fine Time。基于FPGA的TDC之延时线是通过FPGA的逻辑资源实现,由于其可编程性使得Fine Time需要一些特殊处理,本文就是讨论这些所谓的特殊处理。

延时线内插结构

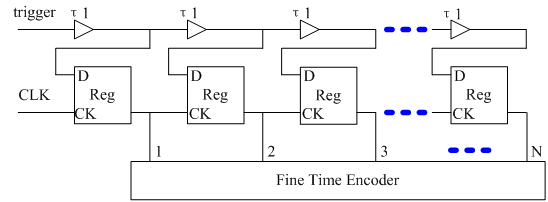

图1是基于FPGA的内插结构TDC原理框图,理想情况下每个延时单元的延时时间τ1是一样的,而且非常小。ALTERA器件的组合逻辑的延时一般都是上百皮秒,不太适合于实现TDC的延时线。比如ALTERA的LCELL模块一般作为寄存器或者逻辑模块之间插入增加延时的基本模块,根据器件以及等级不同LCELL产生的延时时间会不同,但是基本都是在300ps左右。

图1:基于FPGA的TDC结构示意图

实际实现TDC的时候,延时线不能通过逻辑直接实现,利用ALTERA器件内部逻辑的特殊结构,可以使得图1中的延时单元的延时保持在几十皮秒之间,并且整个延时线具有一定的一致性如图2所示。

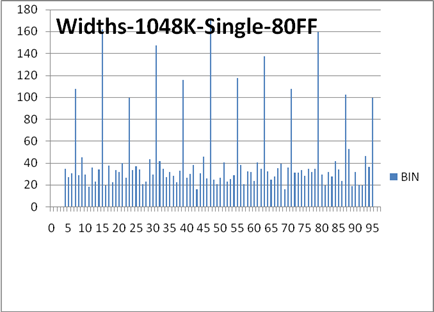

图2是延时线的DNL测试结果,可以看出各个延时单元的延时时间具有一定规律,但是可以肯定的是图1中τ1不是一个恒定值,τ1数值表现形式正如图2一样,利用统计学还可以将图2的DNL进行进一步平滑,这不是本文的重点。仔细观察图2可以发现延时线的头四个延时单元没有延时时间,这是因为头四个延时单元在实现TDC功能的细时间编码的时候根本就没有使用。在实际测试的时候发现如果细时间编码从第一个延时单元开始的话会出现一些问题,后面一节会分析到底会出现什么问题,以及出现这些问题的具体原因。

图2

延时线捕获HIT

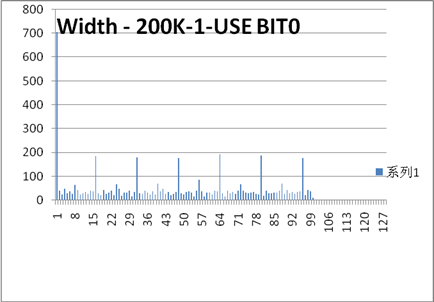

按照正常逻辑,延时线的起始肯定是从第一个延时单元开始,由于延时线内部各个延时单元的延时时间是基本固定且均比较小,而临界位置,即第一个延时单元在捕获HIT的时候存在很大的“uncertainty”即不确定性,从而导致第一个延时单元的延时时间超大,如图3所示。

图3

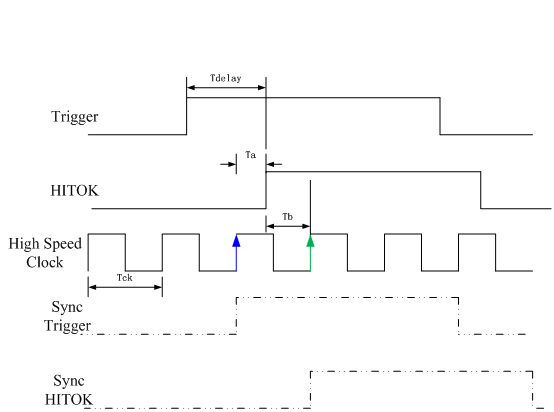

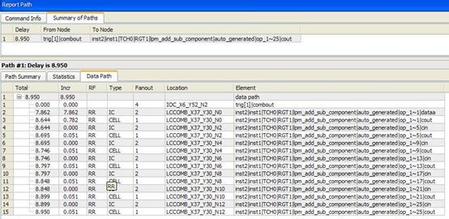

图3中第一个延时单元的延时时间达到700ps左右,而剩下的延时单元和图2几乎无异。为了顺利“捕获”HIT,利用第五个和第六个延时单元里数值变化产生一个捕获信号即HITOK,如图4中信号inst25所示。图5显示了HITOK和HIT(Trigger)以及时钟之间的关系。

图4

图5

图5

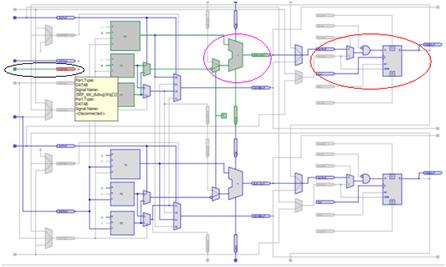

HIT从进入FPGA引脚直到被延时线捕获,这中间的逻辑布线路径以及走线延时不受控制,而且延时时间相对较长,一般都以纳秒级计算,图5中的Tdelay示意出了从HIT到达FPGA引脚到被延时线“捕获”之间的时间。这段路径(path)又大致分为两大部分,一部分是从FPGA引脚到延时线所在的第一个LAB(如图6所示);第二部分是从LAB的里LUT的输入端口(input port)到第一个延时单元的输入(如图7所示)。图7中的黑圈是HIT到达LAB中LUT的端口,从此端口到图7中紫色圈即为上述路径的第二部分,由此HIT才算进入到延时线,后面红色圈住的即为延时线后面的Register阵列中的一个。HIT进入延时线后为了稳定地“捕获”它,所以在编码Fine Time的时候不使用头4个延时单元的数据,因为如果使用就会出现图3所示的状况。因为如果使用第一个延时单元,我们无法严格切割上述第二段路径和第一个延时单元,所以干脆将头4个延时单元一同“cut”掉,这样保留的延时线段是非常纯粹的“延时线”。

图6:HIT从引脚到LAB的路径

图7:HIT从LAB的LUT端口到延时单元路径

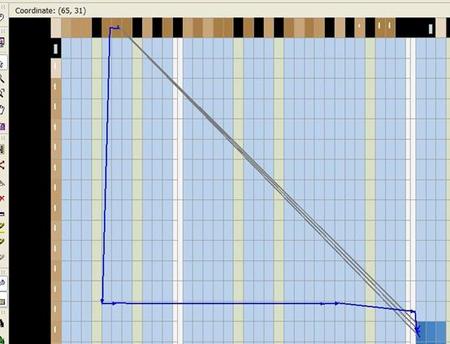

图7所示的路径的延时时间,依据不同的LUT端口,会有不同,但是基本都在几百皮秒以上,所以必须要将其和延时线切割。图8显示了这段路径的具体延时时间,以及相邻部分延时线的各个延时单元的延时时间。可以看到这段路径的延时时间是782ps,而且延时单元的延时时间为51ps,当然这是TimeQuest报告出来的结果,实际运行出来的结果大同小异。

图8

结论

本文分析了基于FPGA的TDC测量结果即Fine Time具体构成,以及在利用FPGA的逻辑资源设计延时线的时候需要注意的一些事项。

用户444716 2013-8-26 08:51

coyoo 2013-8-24 17:47

用户444716 2013-8-24 16:07

coyoo 2013-8-22 09:35

你们没有仔细看我的相关文章,不过我可以提示你一下,LUT只是LE的一部分,还有一部分是Register。至于你的carry-chain为何不能搭太长,这个需要具体问题具体分析,我真的不清楚你遇到的是什么问题。理论上Altera应该不会限制carry-chain的length的

用户444716 2013-8-22 08:55

coyoo 2013-8-15 13:32

用户444716 2013-8-15 10:26

coyoo 2013-5-24 09:23

用户1700348 2013-5-23 22:44

coyoo 2013-5-22 11:34