FPGA下载奇怪问题一例

王敏志

概述

最近困扰笔者一个问题一直没有得到解决,行此文记录备查,同时在博客发布求助于大家,并契合本月测试测量之主题^0^。问题的大概情况是笔者一块板子通过JTAG下载程序的时候出现了问题,目前笔者一共生产了三块板子,只有一块板子出现下载问题。

硬件结构

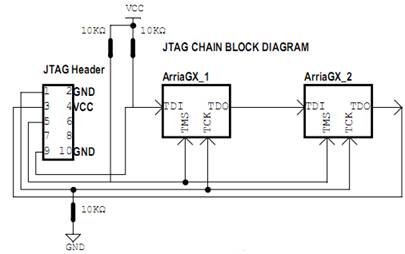

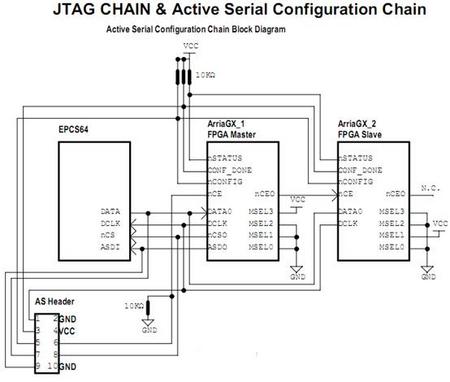

笔者在多篇博文中介绍过单链多FPGA的结构,出现问题的板子就是这种结构。笔者给大家介绍一下自己项目的实际情况,即一个JTAG链有两片FPGA,而这两片FPGA共用一片EPCS64作为配置芯片,如图1所示,而其AS配置电路如图2所示。

图1:单JTAG链多FPGA

图2:一片EPCS64配置两片FPGA

如图2所示,我们看到nCONFIG和nSTATUS都有外部10K电阻上拉,这就是笔者硬件基本结构。

问题细节

问题板子的问题出现在笔者使用SignalTap II下载sof文件到器件时,2片FPGA均下载完后提示我config_done无法“go high”。FPGA也无法正常工作,其实就是FPGA没有正确下载成功。经过测量config_done确实没有被拉高,从图2我们可以看到config_done有很好的外部上拉。

分析ALTERA器件的配置过程以及配置时序图,我们知道上电后nCONFIG和nSTATUS先后有一个低电平,然后nCONFIG被迅速拉高,之后器件释放nSTATUS,nSTATUS开漏结构使得其被外部上拉电阻拉高,nSTATUS的由低到高的变化提示FPGA开始准备接收配置数据,配置完成后FPGA会释放config_done使得config_done被外部拉高得以完成配置过程,而FPGA才可以成功进入用户状态。

笔者测量nCONFIG为高电平,但是nSTATUS为低电平,而且是一上电就是低电平。正常情况是这两个引脚上电瞬间都为低电平,然后nCONFIG被器件迅速释放并被拉高,接着是nSTATUS被释放并被拉高,奇怪的是为什么nSTATUS没有被拉高?

之后更奇怪的事情发生了,折腾一段时间后,笔者已经束手无策了,偶然的机会笔者同事没有使用SignalTap II下载程序,而是使用Programmer来下载,居然下载成功,config_done也正常释放并被拉高,FPGA也能正常工作,但是nSTATUS居然还是保持低电平状态,不可思议。

笔者分析了SignalTap II和Programmer下载程序的异同,相同点是都是JTAG模式下载sof文件,不同点是Programmer能成功下载是因为programmer是点击Start按钮后一个动作同时下载两片FPGA,而SiganlTap II必须一片一片地下载。

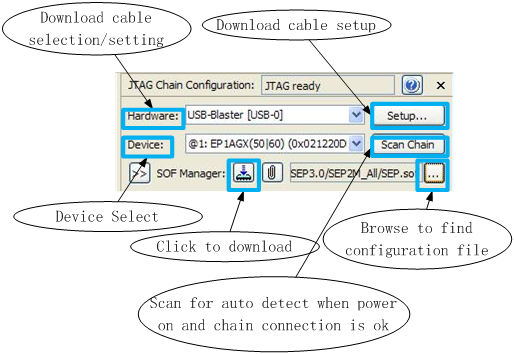

图3:Programmer一次性下载链上器件

如图3所示为Programmer下载器件时,直接勾选所有器件,然后点击Start按钮即可一次性下载所有器件,这样下载就能成功,如果一次勾选一个器件,一片一片下载,结果和SignalTap II一样。但是如图4所示的SignalTap II的下载功能,在“device”菜单框里一次只能选择一个器件下载。

图4:SignalTap II下载功能区

分析及结论

这个问题目前还未找到为何nSTATUS在上电伊始就一直维持为低电平,似乎是器件并没有释放,由于链上有多个器件,不清楚是一片未释放还是两片都未释放,如果是一片未释放,那么到底是哪片也是一个问题。笔者分析应该不是已经释放而上拉未成功造成此问题,因为如果是上拉的问题很好排查并得到解决,笔者也试图改变过上拉电阻,问题依旧。

更困扰笔者的是,nSTATUS一直为低的情况下,链路居然能够下载成功。

参考

[1] Arria GX数据手册

[2] Altera配置手册

[3]

coyoo 2014-8-12 09:21

用户1738735 2014-8-11 20:53

用户433548 2014-4-24 16:01

coyoo 2014-4-23 08:51

用户433548 2014-4-22 16:27