基于FPGA的TDC那些事之粗细计数

王敏志

概述

将时间数字化,也即TDC,可以在FPGA中实现。所谓TDC,通行的办法就是通过在一个时钟周期中进行内插而把时钟周期等分成若干等份。所以一般采用此法实现TDC功能都使用Coarse Time和Fine Time结构,也称粗计数和细计数。

什么是粗计数和细计数呢?

所谓粗计数就是统计时钟周期的计数器,通常为了减少Delay-Line的级数,TDC的粗计数时钟频率会比较高,我们的系统就以250MHz为例。

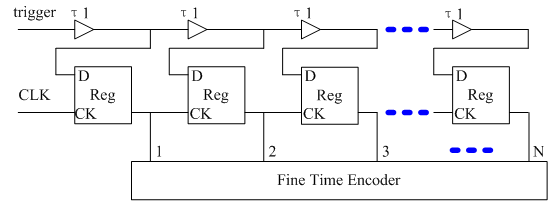

所谓细计数就是某个HIT与相邻时钟沿的间隔,假如250MHz时钟的一个周期中内插100个延时单元,那么每个延时单元表示40ps。那么细计数就相当于表示了HIT和相邻的时钟上升沿之间存在的延时单元的个数。图1显示就是基于内插技术的TDC结构。

图1:基于FPGA的TDC结构示意图

组合粗计数和细计数的问题

传统的基于ASIC的TDC一般都采用双计数器或者格雷码计数器来获取粗时间,而基于FPGA的TDC的粗时间可以使用普通的计数即可。因为在基于FPGA的TDC的基本原理里我们已经知道了HIT和计数器时钟之间的不确定性经过Delay Line后面的Register阵列已经被很好的定义。

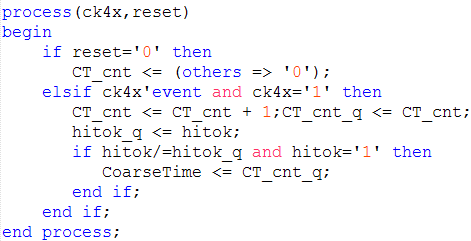

图2给出粗时间计数的代码,实际应用中应该还要加入主机(Host)控制何时启动粗计数器开始计数的控制代码。

细时间就是TDC的测量结果,在实际应用中都是需要将粗时间和细时间组合起来。比如假设粗时间是一个40bit的计数器,细时间是一个8bit的数据,那么最终结果应该是一个48bit的结果。正常情况下,粗时间和细时间是可以直接组合的,但是由于测量方法不同,有时候组合之前还需要对细时间进行转换之后才能组合。

将图1所示的Fine Time Encoder的输出和图2所示代码产生的粗时间合并即为本文重点。

图2:Coarse Time

从图2的代码可知,coarse time是在HITOK(图3中的inst25)的上升沿处记录计数器CT_cnt_q的值得到。而CT_cnt_q为原始计数器锁存一拍而来,下面论述为何要在这里锁存一拍,然后慢慢介绍为何有时候要对细时间进行转换的问题。

Coarse Time寄存一拍

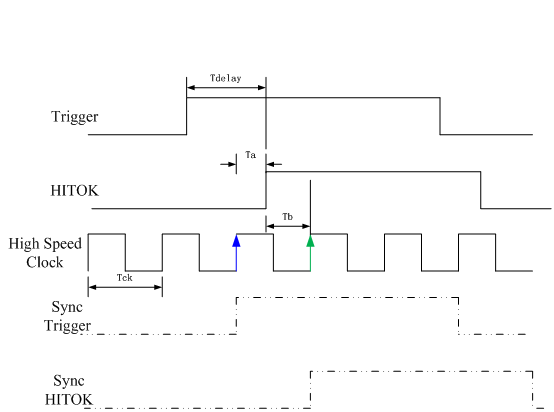

图3:Coarse Time

图4:Coarse Time续

先上两张图片,图3和图4是同一张图片,图3是图4的放大版,可以看清细节。这个图是实际工程run出来的结果。注意上述图片中几个变量,分别是trig[1]、inst25、以及最后三个计数器(CoarseTime、CT_cnt和CT_cnt_q)。trig[1]是外部HIT到FPGA的引脚,inst25是HIT已经被延时线成功捕捉,由图3可知所谓的粗计数延时一拍是指Coarse counter作为粗时间只需计数到HIT被捕捉前一个时钟即可。图5给出了示意图,图中下方虚线就是同步后的HIT以及被“捕捉”的HIT,同图3、4是一样的。

图5

Fine Time调整

图5显示了细时间,即Tb或Ta。如果TDC直接测量出来了Ta,那么完整时间就是直接把粗时间和细时间直接合并即可,如果TDC直接测量出来的是Tb,那么需要先利用Tb计算得到Ta然后再合并粗细时间,即Ta=Tck-Tb,不能直接合并粗时间和Tb。

那么是否可以直接用TDC测量得到Ta呢?答案是肯定的,这里先解释为何需要直接使用Ta而不能直接使用Tb。PET系统中测量某个事件的时间是通过测量事件(或者说trigger)和时间参考之间的间隔而得到该事件的时间信息,所以某个事件的时间信息表示如下

Te=Tstop-Tstart

Tstop=TCstop+TFstop

Tstart=TCstart+TFstart

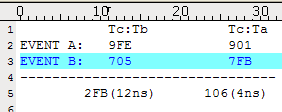

由于TF的满量程范围是4000ps(250MHz,即4ns),如果直接取Tb组合时间信息,那么经过上述运算后本来不符合的事件会变成符合,本来符合的事件会变成不符合(实际误差范围可能接近8ns)。所以为了正确进行符合处理,要么修改TDC测量算法,要么在现有算法基础上对TDC的细时间进行调整。图6给出了一个简单的例子,假设获得了两个事件的时间信息,那么在进行符合运算的时候,如果TDC直接测量结果是Tb,那么是否调整细时间将会得到不同的符合结果,如果符合窗口是8ns,那么左边(未调整)结果是不符合,而右边(调整)结果却是符合的。

图6

结论

经过上述分析,Tb是不能直接组合成TDC的测量结果的。上述分析提到了调整细时间,还有一个更直接的方法就是调整TDC的测量结构,使得TDC测量输出的细时间结果直接为Ta。

coyoo 2016-4-1 08:51

用户1847165 2016-3-31 12:48

coyoo 2015-6-5 09:07

用户1840092 2015-6-4 11:54

coyoo 2013-6-5 10:44

用户403664 2013-6-4 17:13

用户430565 2013-5-9 15:28

coyoo 2013-5-8 09:53

coyoo 2013-5-8 09:51

用户430565 2013-5-7 22:30