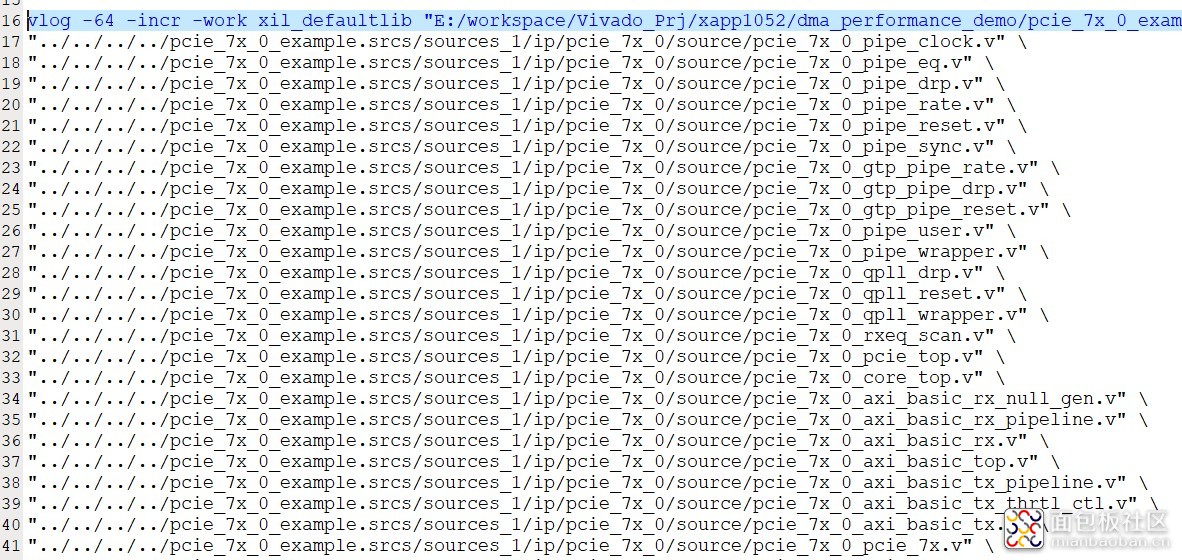

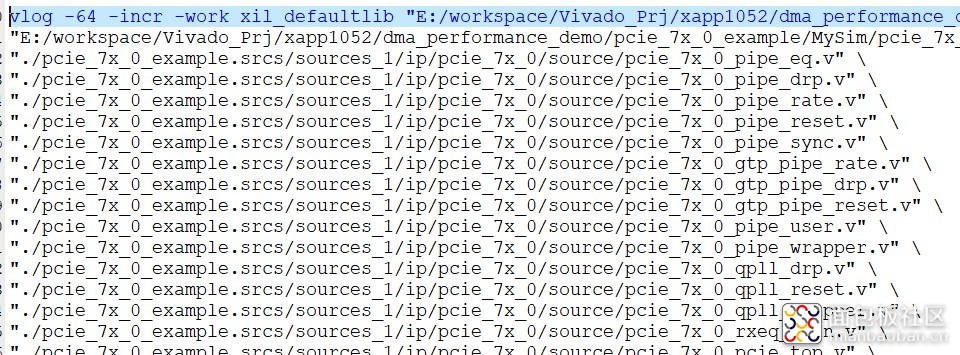

由于xapp1052这个设计并不完备,我需要对其进行修改,但是为了让自己能够回到初始状态,又不希望在这个项目上直接修改,所以想到将其pcie_7x_0_example.srcs目录下所有文件拷贝到其它地方再进行修改并仿真。问题是改动位置后上述vlog语法找寻文件的路径就变了,需要做如下更正:

学过dos系统都知道,“..”表示上一级目录,“.”表示本级目录,如果源文件都在脚本目录下,就不需要指定路径。其实还有一个最笨的办法,就是给每个文件提供完整的绝对路径。

作者: coyoo, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-1010859.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/5

/5

文章评论(0条评论)

登录后参与讨论