概述

FALSE PATH就是我们在进行综合分析时,不希望综合工具进行分析的那些路径。在ALTERA的一个关于TimeQuest的一个培训文档里面解释了什么时候要用到FALSE PATH:

1. 从逻辑上考虑,与电路正常工作不相关的那些路径,比如测试逻辑,静态或准静态逻辑。

2. 从时序上考虑,我们在综合时不需要分析的那些路径,比如跨越异步时钟域的路径。

默认情况下,如果未指定(Altera软件假定所有未指定的时钟的默认频率为1Ghz),TQ假定设计中所有的clock都是相关的,并会分析报告所有路径。所以设计中应该给每个时钟指定其run频率。假如设计中时钟彼此不相关(即为异步时钟),应该为每个异步时钟添加set_clock_groups命令(如“set_clock_groups -asynchronous -group {Rx_clk}”),以给每个异步时钟指定时钟组。另外,在默认情况下如果设计中并未指明false path或者多周期路径的时候,TQ老是试图将所有路径当作有效(valid path)、单周期路径来分析;所以设计中一定要加约束文件,且约束文件中一定要指明false path以及多周期路径;不同时钟域之间的路径上应用false path约束,可以使之成为非有效路径,这样TQ就不会去分析之。

学习研究这个东东,是因为项目中要实现TDC,而TDC的Stop时钟一般需要尽可能高速时钟,而整个系统运行时钟频率一般是100MHz,甚至更低。所以整体设计中必然存在多个时钟域,这个时候,Quartus编译结果时不时给出时序违规的警告,大多数时候都是和TDC的快速时钟有关。这个时候TDC设计者就需要将横跨系统时钟和快速时钟的路径标记出来,最好同时设置为伪路径。所以本文将会探讨伪路径设置及分析。

创建False Path的两种方法

1. 应用set_false_path命令

当已知特定的节点(Nodes)不需要分析的时候使用本命令,比如:

1). All paths from an input pin to a set of registers.

2). All paths from a register to another clock domain.

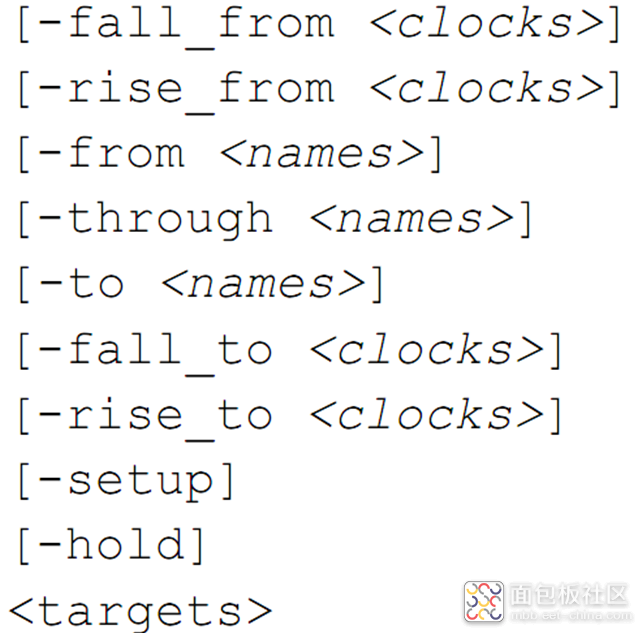

命令选项如图1所示

图1、设置FALSE PTHA命令参数选项

-from和-to用来分别指定源节点(source nodes)和目标节点(target nodes),目标节点可以是clocks、registers、ports、pins或者cells。对于registers,-from必须是源寄存器时钟引脚。指定一个时钟名来约束所有进出本时钟域,这样约束包括了时钟的上升和下降变化,而且比单独约束节点更有效率。

2. 应用set_clock_groups命令

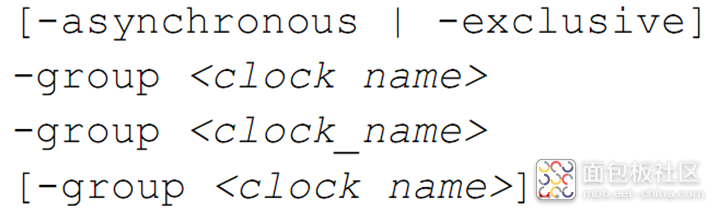

告诉fitter和时序分析器忽略指定的时钟域之间的所有路径,非常适合于时钟多路选择器,另外,本命令相当于在两个时钟域之间的所有路径上设置false paths(-from和-to),具体格式如图2所示。

图2、第二种方法设置false path的参数选项

-group指定的时钟组互相之间是异步的,-asynchronous表示无相位关系,但是时钟同时有效;-exclusive表示时钟不是同时有效,比如时钟多路选择。

False Path培训例子

1. 第一种方法设置false path的例子

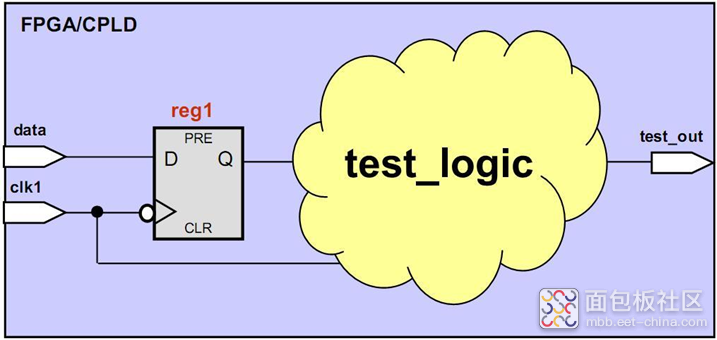

图3中模块test_logic表示一个测试逻辑,它并不是真正实现电路功能,只是为了测试电路功能。所以不希望时序分析器对这些路径进行分析。

图3:无需时序分析的测试逻辑

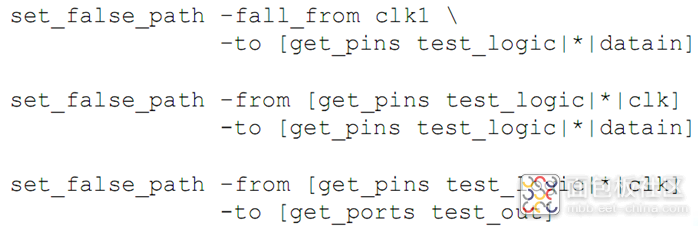

因此设置false path命令如图4所示:

图4:为上述测试逻辑设置伪路径约束

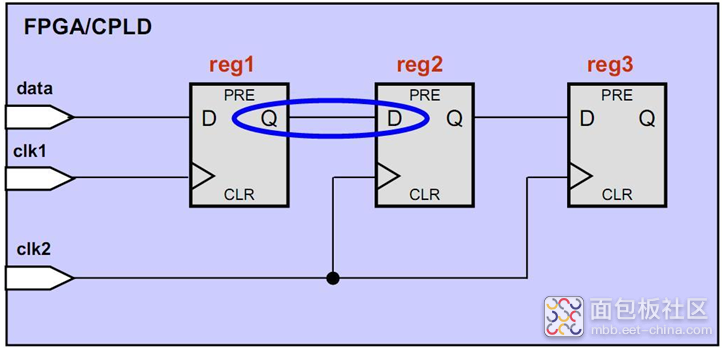

再来看图5是另外一个例子,reg1的输出和reg2的输入跨越了不同的时钟域clk1和clk2,我们不希望综合工具对这这些路径进行分析,就是说这些路径就是我们所说的FALSE PATH:

set_false_path –from [get_pins reg1|clk] –to [get_pins reg2|datain]

图5:跨时钟域路径

2. 第二种方法设置false path的例子

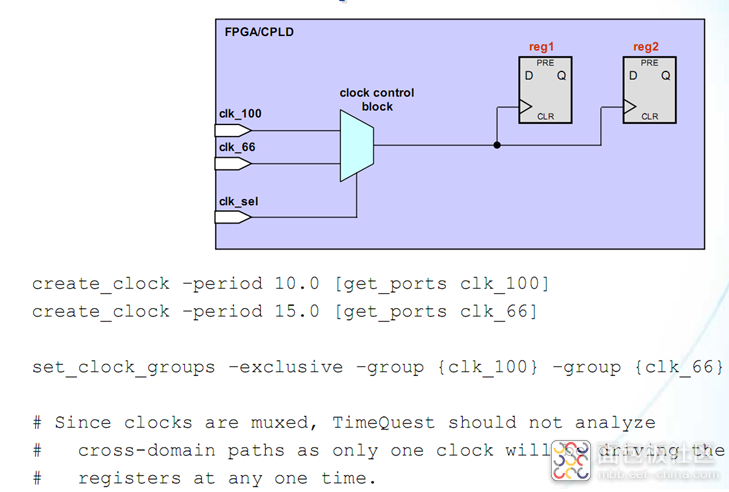

图6中clk_100和clk_66仍然是两个不同的时钟域,所以有图中所示的设置false path的命令。

其实图6中的命令根据上述描述,我知道还可以用第一种方法来实现相同的功能,即

set_false_paths –from [get_clocks clk_100] –to [get_clocks clk_66]set_false_paths –from [get_clocks clk_66] –to [get_clocks clk_100]

图6:不同时钟域建立时钟group

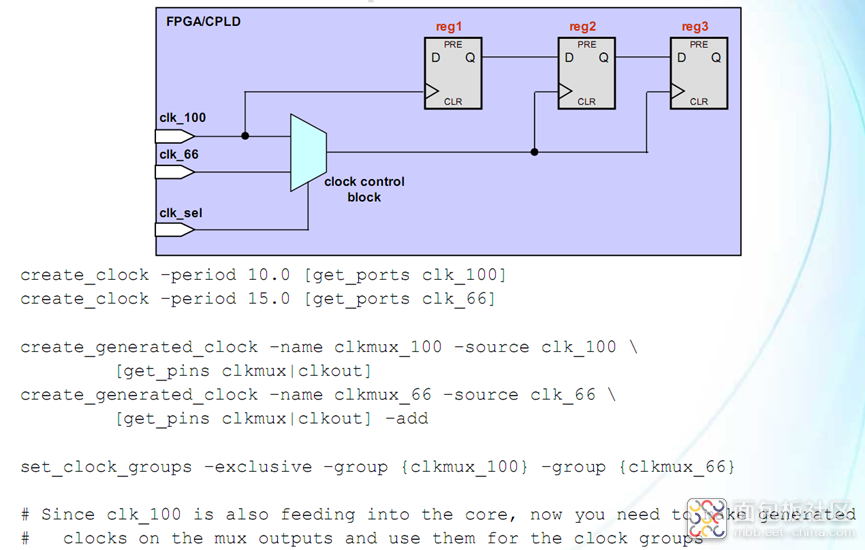

图7和图8分别也是第二种方法的具体体现。

图7

图8

作者: coyoo, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-1010859.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/2

/2

文章评论(0条评论)

登录后参与讨论