SDRAM Controller参数设置<?xml:namespace prefix = o ns = "urn:schemas-microsoft-com:office:office" />

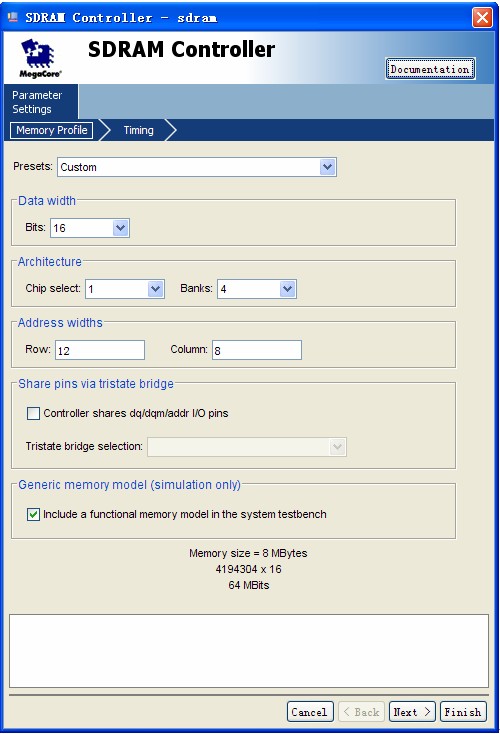

SOPC通过SDRAM controller与板上的SDRAM进行通信,在SOPC中加入SDRAM控制器,弹出如下对话框,里面具体参数说明如下。

<?xml:namespace prefix = v ns = "urn:schemas-microsoft-com:vml" />

一、Memory Profile参数设置

Presets:在该下拉菜单中预设了一些常用的SDRAM的参数,选定某个型号的SDRAM后,会自动修改相应的设置。预设的SDRAM信号有:

■ Micron MT8LSDT1664HG module

■ Four SDR100 8 MByte × 16 chips

■ Single Micron MT48LC<?xml:namespace prefix = st1 ns = "urn:schemas-microsoft-com:office:smarttags" />2M32B2-7 chip

■ Single Micron MT48LC4M32B2-7 chip

■ Single NEC D4564163-A80 chip (64 MByte × 16)

■ Single Alliance AS4LC1M16S1-10 chip

■ Single Alliance AS4LC2M8S0-10 chip

Data Width:数据位宽。

Chip Selects:芯片的片选信号。

Banks:设定DRAM芯片的Bank数目。

由于技术、成本等原因,SDRAM一般不做成一片单一的存储阵列,而是将SDRAM内部分割成几个bank。较早以前是两个,现在基本是四个。所以在寻址是首先要确定在哪一个bank,再选在该bank中的行列地址。

Row:设定行地址线的数量。

Column:设定列地址线的数量。

行地址线和列地址线的和大于总的地址线,这是因为地址线是复用的,在读写操作时,先发送行地址,再发送列地址,有RAS,CAS控制。

Share pins via tristate bridge:选中Controller shares dq/dqm/addr I/O pins后,可以将dq/dqm/addr引脚在下面指定的三态总线上与其他器件复用。

二、Timing参数设置

CAS latency cycles

在CAS发出之后,仍要经过一定的时间才能有数据输出,从CAS与读取命令发出到第一笔数据输出的这段时间,被定义为CL(CAS Latency,CAS潜伏期)。由于CL只在读取时出现,所以CL又被称为读取潜伏期(RL,Read Latency)。CL的单位一般为时钟周期数,具体耗时由时钟频率决定。

Initialization refresh cycles

初始化过程中所需的刷新周期。

Isssue one refresh command every

刷新周期。

DRAM之所以称为DRAM,就是因为它要不断进行刷新(Refresh)才能保留住数据,因此它是DRAM最重要的操作之一。刷新操作一般是用S-AMP先读再写。那么要隔多长时间重复一次刷新呢?目前公认的标准是,存储体中电容的数据有效保存期上限是64ms(毫秒,1/1000秒),也就是说每一行刷新的循环周期是64ms。这样刷新速度就是:行数量/64ms。我们在看内存规格时,经常会看到4096 Refresh Cycles/64ms或8192 Refresh Cycles/64ms的标识,这里的4096与8192就代表这个芯片中每个L-Bank的行数。刷新命令一次对一行有效,发送间隔也是随总行数而变化,4096行时为15.625μs(微秒,1/1000毫秒),8192行时就为7.8125μs。

刷新操作分为两种:自动刷新(Auto Refresh,简称AR)与自刷新(Self Refresh,简称SR)。不论是何种刷新方式,都不需要外部提供行地址信息,因为这是一个内部的自动操作。对于AR, SDRAM内部有一个行地址生成器(也称刷新计数器)用来自动的依次生成行地址。由于刷新是针对一行中的所有存储体进行,所以无需列寻址,或者说CAS在 RAS之前有效。所以,AR又称CBR(CAS Before RAS,列提前于行定位)式刷新。由于刷新涉及到所有L-Bank,因此在刷新过程中,所有L-Bank都停止工作,而每次刷新所占用的时间为9个时钟周期(PC133标准),之后就可进入正常的工作状态,也就是说在这9个时钟期间内,所有工作指令只能等待而无法执行。64ms之后则再次对同一行进行刷新,如此周而复始进行循环刷新。显然,刷新操作肯定会对SDRAM的性能造成影响,但这是没办法的事情,也是DRAM相对于SRAM(静态内存,无需刷新仍能保留数据)取得成本优势的同时所付出的代价。

SR则主要用于休眠模式低功耗状态下的数据保存,此时不再依靠系统时钟工作,而是根据内部的时钟进行刷新操作。在SR期间除了CKE之外的所有外部信号都是无效的(无需外部提供刷新指令),只有重新使CKE有效才能退出自刷新模式并进入正常操作状态。

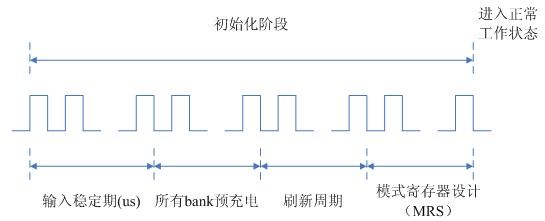

Delay after powerup before initialization

上电后的稳定期。手册上一般给出的是200us,通常我们选择 100us即可。 上电后有一段初始化的工程,时序如下:

Duration of refresh command

每次刷新的持续时间。一般是60或者70ns。对于上文提到每次刷新所占用的时间为9个时钟周期(PC133标准),则9/133MHz=67.7ns。

Duration of prechange command

预充电周期。在发出预充电命令之后,要经过一段时间才能允许发送RAS行有效命令打开新的工作行,这个间隔被称为tRP (Precharge command Period,预充电有效周期)。tRP的单位一般也是时钟周期数,具体值视时钟频率而定。ezNiosDK的用户可以选择 20ns。

实际上,预充电是一种对工作行中所有存储体进行数据重写,并对行地址进行复位,同时释放芯片内部的比较器(重新加入比较电压,一般是电容电压的1/2,以帮助判断读取数据的逻辑电平),以准备新行的工作。具体而言,就是将放大/驱动比较器中的数据回写。存储单元中的电容容量很小,即使是没有工作过的存储体也会因行选通而使存储电容受到干扰,所以也需要进行读后重写。

ACTIVE to READ or WRITE delay

在发送列读写命令时必须要与行有效命令有一个间隔,这个间隔被定义为tRCD,即RAS to CAS Delay(RAS至CAS延迟),也可以理解为行选通周期,这应该是根据芯片存储阵列电子元件响应时间(从一种状态到另一种状态变化的过程)所制定的延迟。tRCD是SDRAM的一个重要时序参数。广义的tRCD以时钟周期(tCK,Clock Time)数为单位,比如tRCD=2,就代表延迟周期为两个时钟周期,具体到确切的时间,则要根据时钟频率而定,对于运行在100M的SDRAM, tRCD="2",代表20ns的延迟,对于PC133则为15ns。

Access time

访问时间。

从数据I/O总线上有数据输出之前的一个时钟上升沿开始,数据即已传向读出放大器,也就是说此时数据已经被触发,经过一定的驱动时间最终传向数据I/O总线进行输出,这段时间我们称之为tAC(Access Time from CLK,时钟触发后的访问时间)。tAC的单位是ns,对于不同的频率各有不同的明确规定,但必须要小于一个时钟周期,否则会因访问时过长而使效率降低。比如PC133的时钟周期为7.5ns,tAC则是5.4ns。需要强调的是,每个数据在读取时都有tAC,包括在连续读取中,只是在进行第一个数据传输的同时就开始了第二个数据的tAC。

Write recover time

回写延迟。

写操作虽然是0延迟进行,但每笔数据的真正写入则需要一个足够的周期来保证,这段时间就是写回周期(tWR)。所以预充电不能与写操作同时进行,必须要在tWR之后才能发出预充电命令,以确保数据的可靠写入,否则重写的数据可能是错的,这就造成了写回延迟。

文章评论(3条评论)

登录后参与讨论-

用户1332143 2009-08-16 21:47

- 时序电路亚稳态分析

- 这篇文章是我对电子设计中,亚稳态问题的一种分析和总结。文章通过对数字电路中器件的工作机制的介绍,引出亚稳态问题的发生机制。并通过对亚稳态问题发生机制的探讨,用以得到一种能够清楚地,有的放矢地解决亚稳态...

-

用户1332143 2009-08-16 10:52

- 【推荐】ADF4350配置软件下载

- p class="MsoNormal" style="MARGIN: 0cm 0cm 0pt"> 随着现代半导体工艺的不断发展, 几十纳米级的CMOS工艺给数字电路带来了很大的恩惠, 但对模拟...

-

用户1332143 2009-08-14 12:47

- 【原创】基于NiosII及FT245BM的USB接口设计

- 以前做的一个项目,FPGA接收AD采集数据后,通过串口发送回PC机,由于串口传输速率较低,对于实时性要求较高的场合不太适用,因此站长选用FT245BM芯片来实现USB接口传输,本文主要讲解FT245B...

-

用户1332143 2009-08-13 14:56

- 【原创】MAXII:UFM中晶振的使用

- MAXII系列CPLD中带有UFM模块,本文主要讲解UFM中晶振的使用,具体内容请点击下面链接MAXII:UFM中晶振的使用...

-

用户1332143 2009-03-01 21:53

- 【原创】如何使用FPGA进行信号调制

- 最近要做一个通信收发系统项目,以前对收发器的射频前段关注的比较多,而对基带部分的信号处理一直没有仔细研究。因此,正好借这个项目,熟悉整个基带部分的信号处理流程。 基带部分主要...

-

用户1332143 2009-02-27 21:56

- 寒假回来——FPGA市场评论

- 寒假在家里电脑不能上网,好久没来更新自己的博客了,首先感谢大家对我博客的支持。回来后马上开始了一个863项目,一直没有时间来写博客,今天总算有时间,上来看看。回来这段时间关注了下FPGA的相关新闻,发...

/3

/3

loodao_812158451 2014-10-23 09:23