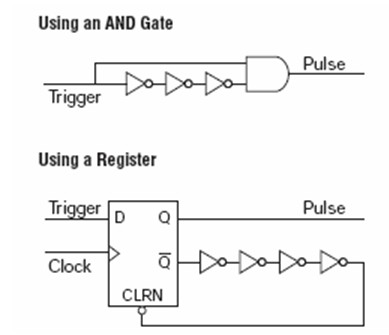

在很多情况下,需要根据FPGA的外部输入信号产生一个脉冲去触发内部逻辑或外部器件,在ASIC中经常使用异步脉冲发生器,如下图所示:

不过在FPGA中尽量避免使用异步时序设计,因为异步电路在不同的PVT(process, voltage, and temperature)条件下,结果会有一些差异。下面推荐一种同步脉冲发生器的设计。

module demo(input clk,input trig,output pulse);

reg temp1,temp2;

always @(posedge clk)

begin

temp1 <= trig;

temp2 <= temp1;

end

assign pulse = temp1 & ~(temp2);

endmodule

综合后通过Technology map Viewer(Post-mapping)查看技术映射图:

仿真结果如下:

在trig中输入一段高电平,在pulse引脚输出一个周期的脉冲,如果要使脉冲的宽度加大,可以在程序中多加一个temp寄存器,这样输出的脉冲宽度会加大。

/4

/4

用户1356205 2009-2-19 11:01