我们在设计电源平面的时候,首先考虑到的基本原则是电源平面和地平面保持较小的介质厚度,可以增大整个平面的电容量,从而保证良好的电源去耦效果。然而对于本身板厚度就很小的叠层设计来说,按这个规则达到了减小耦合距离,增大电容的作用呢?还是需要考量到供电过孔的残桩效应带来的影响呢?这两者,who get the better performance ?

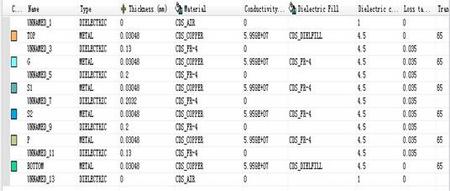

我们通过下面的叠层设计来验证这两个问题?我们采用如下的验证叠层,Stcakup total thickness为1.04mm,6 layers,验证的叠层电气属性分布:SGSSPS vs SGPSSS,板子尺寸为15mmx30mm;

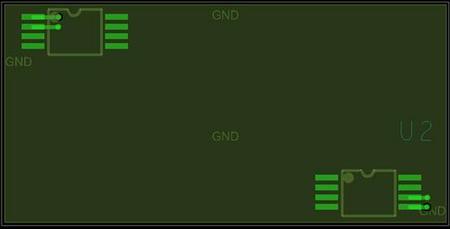

仿真测试的PCB为

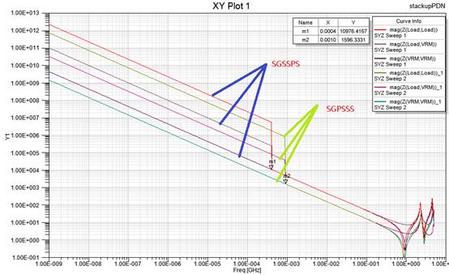

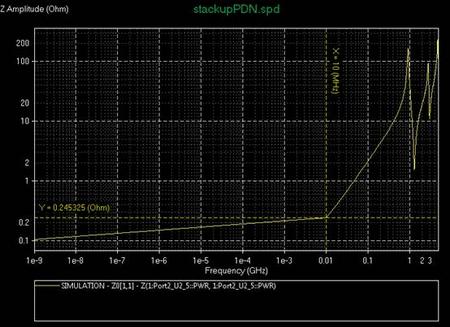

U1的供电端为VRM,U2为负载端;仿真结果对比:

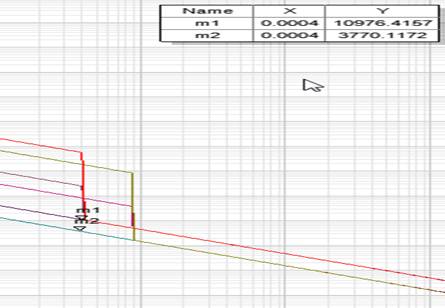

可以看出当两个平面相邻时可以获得更低的Z参数,更好的去耦功能,两者某个频点的差值为

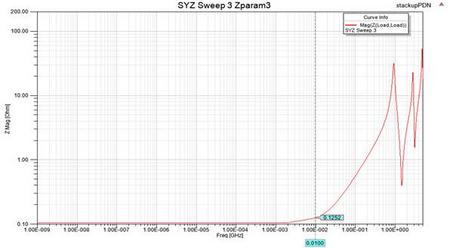

在SGPSSS结构中将VRM设置为0.1ohm电阻, sigrity U2 port的结果

Siwave的结果:

Siwave仿真的结果比sigrity小很多(why??),但是两者谐振点的频率位置比较接近。

all right reserved by mark,转载请注明出处,tks!

/4

/4

文章评论(0条评论)

登录后参与讨论